# Hardware Implementation of an OFDM Transceiver for 802.11n systems

# Rajesh S. Bansode & Prajakta Borole

**Abstract** – The best approach for real time application to achieve high throughput and network capacity for fourth generation wireless local area networks is to combine MIMO wireless technology with OFDM. This paper focuses on high level Matlab Simulink 4 x 4 spatially multiplexed (SM) MIMO OFDM transceiver encoded at  $\frac{1}{2}$  rate using 64 size FFT which is designed and implemented on Spartan Virtex 6 FPGA board. The hardware co-simulation, RTL Schematics, Test Bench and VHDL codes for all the blocks and for the complete 4 X 4 MIMO OFDM model are obtained to verify its functionality.

**Index Terms**—Field Programmable Gate Array, Matlab Simulink, Multiple Input Multiple Output, Orthogonal Frequency Division Multiplexing, Space Time Block Code, Spatial Multiplexing, System Generator and Xilinx.

# **1** INTRODUCTION

Orthogonal Frequency Division Multiplexing (OFDM) is a multicarrierbased technique for mitigating ISI to improve capacity in the wireless system with spectral efficiency. Multiple-Input Multiple-Output (MIMO) systems have achieved attention as it promises to increase capacity and performance with acceptable BER proportionally with the number of antennas [11]. The combination of MIMO-OFDM is beneficial.

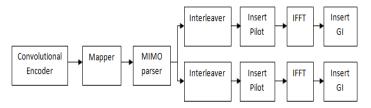

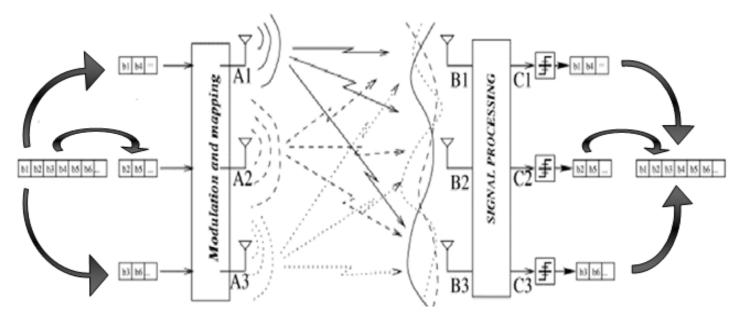

The MIMO OFDM system comprises of transmitter and receiver sections. The transmitter comprises blocks such as convolutional encoder, mapper, parser, and IFFT. The data encoded at a specific rate like ½ or 2/3 and then is modulated using various modulation schemes such as BPSK/ QPSK/QAM [7]. This signal is then parsed into two or more channels and later it is converted into time domain and transmitted. The operations of receiver blocks are opposite to that of transmitter to receive the actual signal.

Fig 1.1 MIMO OFDM Transmitter Block diagram

The paper is organized in the order mentioned as follows: The Section 2 describes about MIMO and MIMO based techniques like STBC and SM.

Fig.1.2 MIMO OFDM Receiver Block diagram

Section 3 describes the implementation of  $4 \times 4$  MIMO system using Matlab Simulink and Xilinx software. In Section 4 factors affecting data rate and complexity of the system are discussed. The Section 5 describes about results and conclusions.

# 2 MIMO

In MIMO system multiple antennas are employed at the transmitter and the receiver. MIMO transmits and receives two or more data streams through a single radio channel. Thereby the system can deliver two or more times the data rate per channel without additional bandwidth or transmit power [1].The addition of multiple antennas at the transmitter combined with advanced digital signal processing based algorithms and the receiver yields significant advantage in terms of capacity and diversity [10].

Space-time block coding and spatial multiplexing are MIMO based techniques that provide link quality and high capacity in the system. STBC and SM can be combined to give a transmission scheme that will maximize the average data rate over the MIMO channel and guarantee a minimum order of diversity benefit for each stream [13].

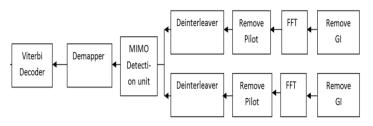

The SIMO 1 x 4 system provides lower capacity than MIMO 2 x 2 system while still higher capacity is achieved in case of 4 x 4 MIMO system [12]. Therefore the capacity of system increases linearly with increased number of antennas.

For a memory less Single Input Single Output (SISO) system the capacity is given by

$$C = \log_2 \left(1 + \rho |h^2|\right) \quad b/s/Hz \tag{1}$$

Where h is the normalized complex gain of a fixed wireless,  $\rho$  is the SNR at any Receiver antenna.

The capacity for a Single Input Multiple Output (SIMO) system is given by

$$C = \log_2 \left( 1 + \rho \sum_{i=1}^{M} |\mathbf{h}_i|^2 \right) \, \mathrm{b/s/Hz}$$

(2)

Where h<sub>i</sub> is the gain for receiver antenna i.

The capacity for a multiple input–single-output (MISO) system with N transmitter antennas is given by

$$C = \log_2 \left( 1 + \frac{p}{N} \sum_{i=1}^{N} ||\mathbf{h}_i||^2 \right) \mathbf{b} / \mathbf{s} / \mathbf{Hz}$$

(3)

The capacity for a MIMO system with N Transmitter and M Receiver antennas is given by

$$C = \log_2 \left[ \det \left( I_M + \frac{p}{N} H H^* \right) \right] b/s/Hz$$

(4)

Where (\*) means transpose-conjugate and H is the M x N channel matrix.

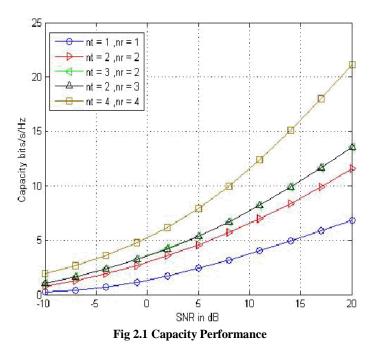

# 2.1 Space-Time Block Coding

Space-Time Block Coding (STBC) is a scheme in which the information is transmitted simultaneously on different antennas. Alamouti proposed an orthogonal block code using two transmitters and two receiver (N ×  $M = 2 \times 2$ ). Every two time slots, two symbols are transmitted simultaneously over two antennas. At the first symbol time, s1 is transmitted from antenna 1, and s2 from antenna 2. Next, -s2 \* is transmitted from antenna 1, and s1\* from antenna 2 at the second symbol time [5], [9]. The code has full diversity as the same information is transmitted over independent paths to mitigate fading. Using simple linear combining, the transmitted signal can be decoded. The very simple structure and linear processing of the Alamouti construction makes it very attractive scheme.

Fig 2.2 Space-Time Block Coding

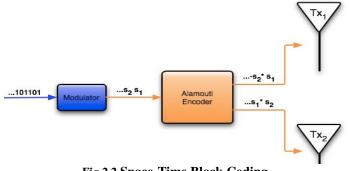

### 2.2 Spatial Multiplexing

The concept of spatial multiplexing (SM) is different from that of spacetime block coding method. The SM provides high throughput as compared to STBC at higher SNR. The spatial multiplexing method uses multiple antennas at the transmitter and receiver to provide a linearly increasing capacity gain with increased number of antennas. In this system a high rate bit stream is decomposed into N independent bit sequences which are then transmitted using multiple antennas. These signals get mixed in the channel as they use same frequency spectrum. At the receiver individual bit streams are separated, estimated and merged together to yield the original signal [14]. Thus MIMO transmits N streams through a single channel, thereby can deliver N or more times the data rate per channel without additional bandwidth or transmit power. The 4 x 4 MIMO transceiver model in this paper implements spatial multiplexing scheme.

The input output relation for N transmitter antennas and M receiver antennas MIMO system is given by

$$y = H x + n \tag{5}$$

Where  $x = [x_1, x_2, ..., x_N]^T$  is the N x 1vector of transmitted symbols, y, n are the M x 1 vectors of received symbols and noise respectively and H is the M x N matrix of channel coefficients [13].

For a 2 x 2 MIMO channel

$$Y_1 = h_{11} x_1 + h_{12} x_2 + n_1$$

(6)

$Y_2 = h_{21} x_1 + h_{22} x_2 + n_2$  (7)

$$\begin{bmatrix} y_1 \\ y_2 \end{bmatrix} = \begin{bmatrix} h_{11} & h_{12} \\ h_{21} & h_{22} \end{bmatrix} \begin{bmatrix} x_1 \\ x_2 \end{bmatrix} + \begin{bmatrix} n_1 \\ n_2 \end{bmatrix}$$

(8)

Similarly for a N x M MIMO system the H matrix is given as

$$H = \begin{bmatrix} h_{11} & h_{12}h_{13} & \dots & h_{1N} \\ h_{21} & h_{22}h_{23} & \dots & h_{2N} \\ h_{31} & h_{32}h_{33} & \dots & h_{2N} \\ \vdots & \vdots & \vdots & \ddots & \vdots \\ h_{M1}h_{M2}h_{M3} & \dots & h_{MN} \end{bmatrix}$$

(9)

$$Y_1 = h_{11} x_1 + h_{12} x_2 + h_{13} x_3 + \dots + h_{1N} x_{4+} n_1$$

(10)

$$f_2 = h_{21} x_1 + h_{22} x_2 + h_{23} x_3 + \dots + h_{2N} x_4 + n_2$$

(11)

$$\mathbf{I}_{3} = \mathbf{I}_{31} \mathbf{X}_{1} + \mathbf{I}_{32} \mathbf{X}_{2} + \mathbf{I}_{33} \mathbf{X}_{3} + \dots + \mathbf{I}_{3N} \mathbf{X}_{4} + \mathbf{I}_{3}$$

(12)

: : : : : : : : : :

$$Y_{M} = h_{M1} x_{1} + h_{M2} x_{2} + h_{M3} x_{3} + ... + h_{MN} x_{N} + n_{M}$$

(13)

$$\begin{bmatrix} y_1 \\ y_2 \\ y_3 \\ \vdots \\ y_M \end{bmatrix} = \begin{bmatrix} h_{11} & h_{12}h_{13} & \dots & h_{1N} \\ h_{21} & h_{22}h_{23} & \dots & h_{2N} \\ h_{31} & h_{32}h_{33} & \dots & h_{3N} \\ \vdots & \vdots & \ddots & \vdots \\ h_{M1}h_{M2}h_{M3} & \dots & h_{MN} \end{bmatrix} \begin{bmatrix} x_1 \\ x_2 \\ x_3 \\ \vdots \\ x_N \end{bmatrix} + \begin{bmatrix} n_1 \\ n_2 \\ n_3 \\ \vdots \\ n_M \end{bmatrix}$$

(14)

# 3. 4 x 4 MIMO SYSTEM DESCRIPTION

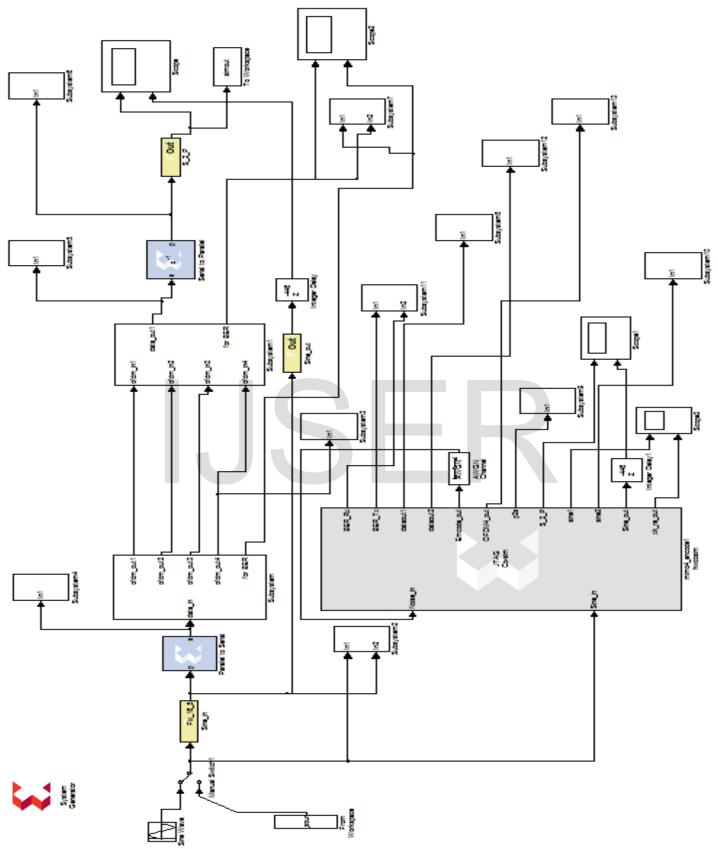

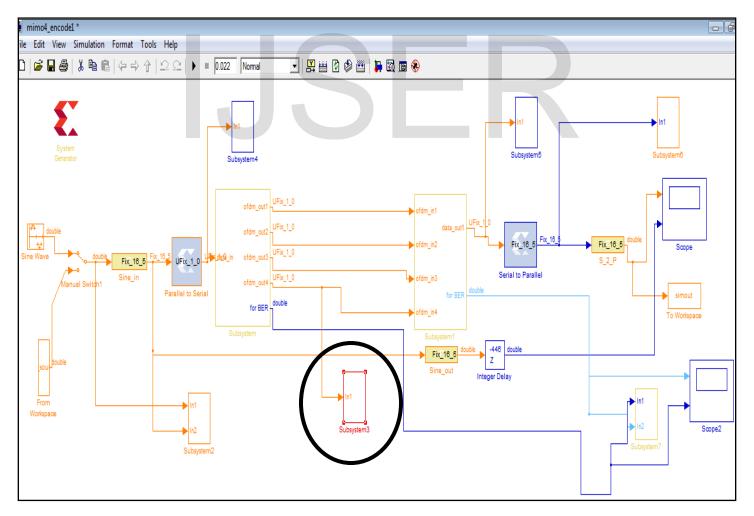

The 4 x 4 MIMO model is illustrated in figure 3.1. The system is designed and implemented on a high level mathematical modeling of Matlab Simulink. The reason for selecting Matlab Simulink is because of its real time environment which resembles the real time design. The system is made of two important parts of transmitter and receiver. The next two sub sections describe each part of the transceiver.

A real time audio signal is applied to the workspace with the help of a manual switch. The input sampled voice signal is then passed through the parallel to serial convertor and is given to the Subsystem. The subsystem is the transmitter module while subsystem 1 is the receiver module. The scrambler and descrambler are used for clock recovery. The transmitter has various parts where the data bits are encoded using the convolutional encoder.

Fig 2.3 Spatial Multiplexing scheme

The encoded bits then are punctured and mapped using one of the standard constellations. Next the bits are fed to the parser which split outs the single channel into four streams and then it is given at the receiver. The receiver functions in the reverse order as that of the transmitter by combining the four streams into one and de-mapping and decoding the bits to get the actual audio signal.

A real time audio signal is applied to the workspace with the help of a manual switch. The input sampled voice signal is then passed through the parallel to serial convertor and is given to the Subsystem. The subsystem is the transmitter module while subsystem 1 is the receiver module. The scrambler and descrambler are used for clock recovery. The transmitter has various parts where the data bits are encoded using the convolutional encoder. The encoded bits then are punctured and mapped using one of the standard constellations. Next the bits are fed to the parser which split outs the single channel into four streams and then it is given at the receiver. The receiver functions in the reverse order as that of the transmitter by combining the four streams into one and demapping and decoding the bits to get the actual audio signal.

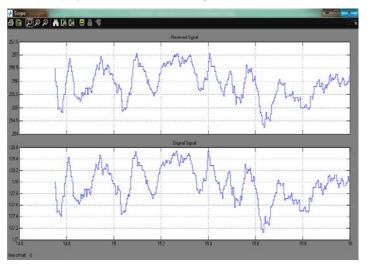

A scope is connected where the first plot is for output of 4 x 4 MIMO model whereas the second plot is just the input signal applied to the system to verify the same signal is reproduced at the receiver side. A SNR of 15 dB is added along with displays, scopes at different points to understand functioning of the entire system.

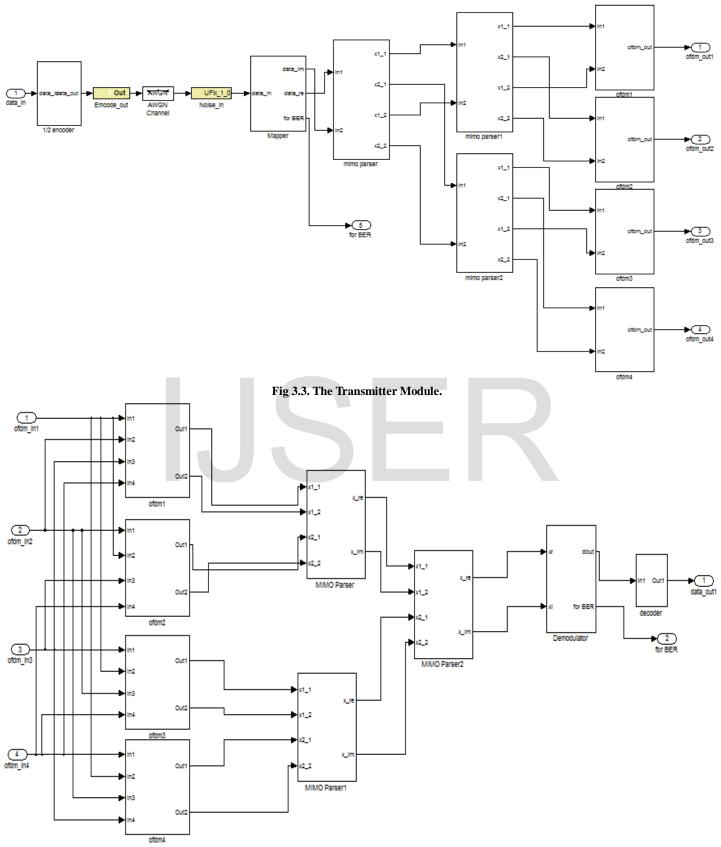

## 3.1 The Transmitter Subsystem

The transmitter subsystem as in figure 3.3 mainly comprises of convolutional encoder, mapper, MIMO parser and IFFT. The sampled input voice bits are encoded using a ½ convolutional encoder, truncated, concated and is given to the mapper. The ROM\_Imaginary(ROM\_Imag), ROM\_Real altogether forms QAM mapper. The ROM\_Imag provides the value on imaginary axis while ROM\_Real provides the value on real axis giving up the points on different quadrants.

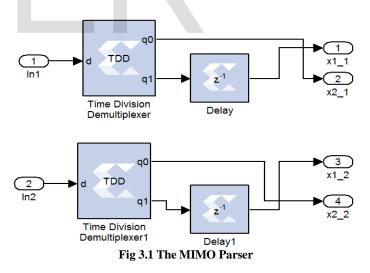

**MIMO Parser:** The ROM-Imag and ROM\_Real are fed to the MIMO parser as In 1 and In 2 respectively. The main purpose of using a MIMO parser is to split the single stream input into two streams.

**Ofdm block:** The first ROM\_Imag and first ROM\_Real i.e. the first and third outputs of MIMO parser1 are applied as inputs to the ofdm 1 block. A 64 size IFFT transforms the signal into time domain [8]. The pilot and guard interval subcarriers are automatically inserted and the output is given at ofdm\_out. The ofdm 2 block performs exactly same as that of ofdm 1 block and extracts the ROM\_Imag and ROM\_Real inputs for mimodeparser. The ofdm 3 and 4 performs exact same as that of ofdm 1 and 2 respectively to be fed as inputs for mimodeparser.

#### 3.2 The Receiver Subsystem

In receiver subsystem as shown in figure 3.4 the outputs of four streams from transmitter are fed as input to ofdm blocks. In ofdm1 FFT performs the exact reverse operation as that of the IFFT. It removes the pilot and guard subcarriers and extracts the ROM\_Imag and ROM\_Real inputs for mimodeparser. The ofdm 2 block performs exactly same as that of ofdm 1 block and extracts the ROM\_Imag and ROM\_Real inputs for mimodeparser. The ofdm 3 and 4 performs exact same as that of ofdm 1 and 2 respectively to be fed as inputs for mimodeparser 1.

Fig. 3.2. Top Level Design of a 4 x 4 MIMO model

Fig 3.4. The Receiver Module

IJSER © 2013 http://www.ijser.org

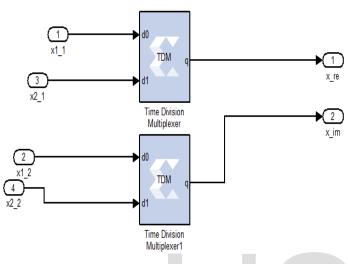

**MIMO Deparser:** At the transmitter side the signal is divided whereas at the receiver signals are being combined together. The combination of two or more signals is deparsing. The MIMO Deparser uses two Time Division Multiplexers. Two ROM\_Imag signals are combined to form a single ROM\_Imagl while the two ROM\_Real signals are combined to form a single ROM\_Real signals. The output of mimoDeparser and mimoDeparser 1 are connected to mimoDeparser 2 so that the splitted streams can be combined together and ROM- Imag and ROM\_Real signals can be obtained.

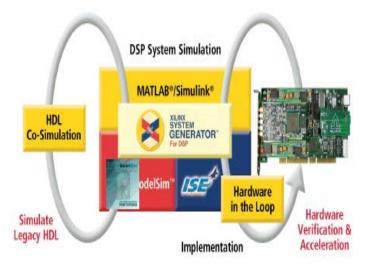

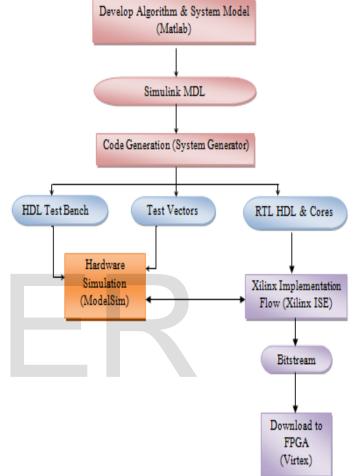

flexibility to design flow [4]. Simulink and Xilinx System Generator create bit-true. The Xilinx Integrated Software environment (ISE) is used as the synthesizer in the design flow diagram. Model Sim is used to verify the hardware simulation of the blocks by using test vectors generated by System Generator or HDL test benches. Finally synthesis and performance results of the blocks are reported using ISE, and bit streams are generated to program the FPGA board [2].

Fig 3.5. The MIMO De-parser

**Demodulator and Decoder:** The ROM\_REAL and ROM\_IMAG signals are fed as inputs  $X_r$  and  $X_i$  to the demodulator respectively. A Matlab code is used for QAM demodulator and is given out at  $D_{out}$ . The decoder which consists of serial to parallel block and a decoder block. The first plot is for output of 4 x 4 MIMO model whereas the second plot is just the input signal applied to the system to verify the same signal is reproduced at the receiver side.

# 4 METHODOLOGY

Fig 4.1. Implementation Methodology

The algorithm of each block using Matlab Simulink is implemented by use of constructing block diagrams in Simulink. VHDL code is imported into Simulink via the Xilinx System Generator block set, which gives

Fig 4.2. Flow Diagram

#### **5** RESULTS AND DISCUSSIONS

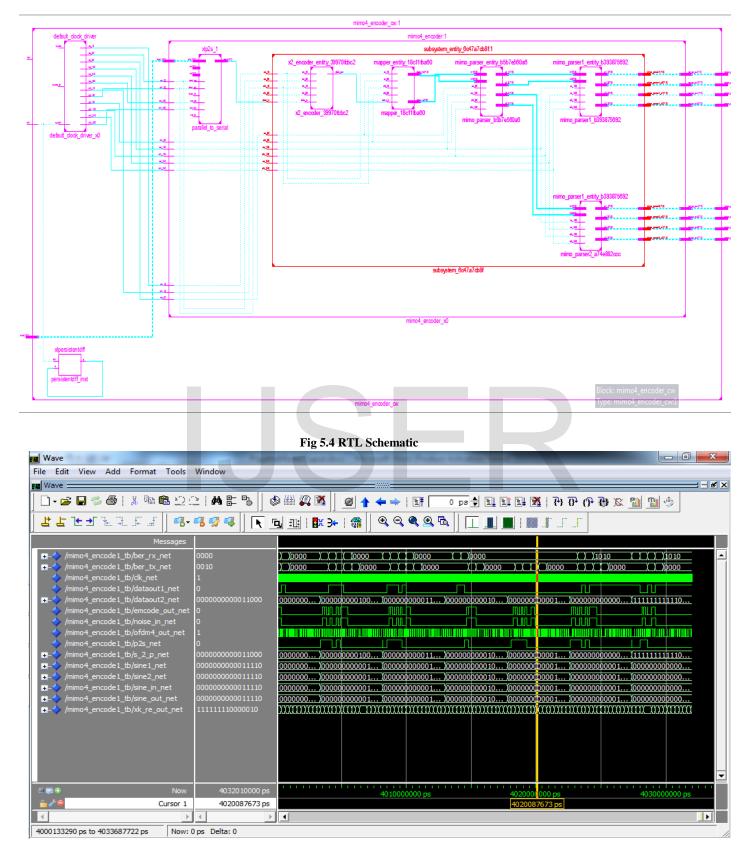

High data rates up to 216 Mbps are achieved by transmitting large number of bits per symbol. Thus for high data rates, higher order QAM is used. However, the higher the number of bits per symbol, the more susceptible the scheme is to the Inter-Symbol Interference and noise [6].The hardware co-simulation, VHDL codes, RTL Schematics, Test Bench, and data rate variations are obtained for the 4 X 4 MIMO OFDM model to verify the same.

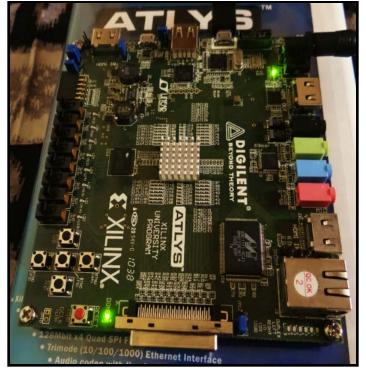

#### 5.1 Hardware Co-simulation

The DONE LED glows indicating that the FPGA is now ready to be programmed. The output of the scope can be seen in the Figure 5.2 where the first waveform is the signal which has been achieved at the output of model i.e. received signal and the second waveform is the actual voice signal which was been fed as input to the model.

Fig 5.1 FPGA ready for programming

# 5.2 VHDL Code, RTL Schematic and Test Benches Generation

The VHDL codes and RTL schematics are generated for the entire model using the ISE Project Navigator by selecting the implementation option. The detailed RTL schematics can be viewed for all the sub models inside the main model. The test bench simulation is obtained with help of ModelSim verifying the correctness of the implemented model.

Fig 5.2 MIMO output and input signal

| ISE [    | ISE Project Navigator (M.70d) - D:\Mimo_Prajakta\MIMO_FINAL\mimo4_encode1_cw.xise - [mimo4_encode1_cw.vhd] |          |            |                                                                                                      |  |  |  |  |  |  |

|----------|------------------------------------------------------------------------------------------------------------|----------|------------|------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|          | ile Edit View Project Source Process Tools Window Layout                                                   | He       | elp        | - #×                                                                                                 |  |  |  |  |  |  |

|          | 🖻 🖥 🖉 🐰 🗅 🗋 🗙 🗩 🖉 🖉 🖉                                                                                      | )        |            | h 🗖 🖬 🥵 🥕 😵 🕨 🕱 🛠 💡                                                                                  |  |  |  |  |  |  |

| Desig    | יח ↔ □ & ×                                                                                                 | €        | 519        | ce: in std logic := '1';                                                                             |  |  |  |  |  |  |

| *        | View: 💿 🔯 Implementation 🔘 树 Simulation                                                                    | ÞĒ       | 520        | <pre>clk: in std_logic; clock period = 10.0 ns (100.0 Mhz)</pre>                                     |  |  |  |  |  |  |

|          | Hierarchy                                                                                                  | _        | 521        | noise_in: in std_logic;                                                                              |  |  |  |  |  |  |

|          | i∰ immo4_encode1_cw                                                                                        | Ξ        | 522        | <pre>sine_in: in std_logic_vector(15 downto 0); base mut std_logic_vector(2 downto 0);</pre>         |  |  |  |  |  |  |

| 8        | □ mmot_cncode_cw                                                                                           | 5        | 523<br>524 | <pre>ber_rx: out std_logic_vector(3 downto 0);<br/>ber tx: out std logic vector(3 downto 0);</pre>   |  |  |  |  |  |  |

|          | Imassigned User Library Modules                                                                            | Ξ        | 525        | dataout1: out std logic;                                                                             |  |  |  |  |  |  |

| —        | 🖶 🔚 📲 mimo4_encode1_cw - structural (mimo4_encode1_cw.vhd)                                                 | 2        | 526        | dataout2: out std logic vector(15 downto 0);                                                         |  |  |  |  |  |  |

| €        | 🗄 🖫 🙀 xlclockenablegenerator - behavior (mimo4_encode1.vhd)                                                | <u> </u> | 527        | emcode out: out std logic;                                                                           |  |  |  |  |  |  |

|          |                                                                                                            | ٨        | 528        | ofdm4_out: out std_logic;                                                                            |  |  |  |  |  |  |

| ¥        |                                                                                                            | %        | 529        | p2s: out std_logic;                                                                                  |  |  |  |  |  |  |

|          | No Processes Running                                                                                       | *        | 530        | <pre>s_2_p: out std_logic_vector(15 downto 0);</pre>                                                 |  |  |  |  |  |  |

| <u> </u> |                                                                                                            |          | 531        | <pre>sine1: out std_logic_vector(15 downto 0);</pre>                                                 |  |  |  |  |  |  |

| ŢΪ       | Processes: mimo4_encode1_cw - structural *                                                                 | *        | 532        | <pre>sine2: out std logic vector(15 downto 0);</pre>                                                 |  |  |  |  |  |  |

| Ξű.      | 🖮 🖓 🚹 Synthesize - XST                                                                                     |          | 533<br>534 | <pre>sine_out: out std_logic_vector(15 downto 0); xk re out: out std logic vector(14 downto 0)</pre> |  |  |  |  |  |  |

|          | - 😨 View RTL Schematic                                                                                     |          | 535        | ):                                                                                                   |  |  |  |  |  |  |

| 7        |                                                                                                            |          | 536        | end mimo4 encode1 cw;                                                                                |  |  |  |  |  |  |

|          | Check Syntax                                                                                               |          | 537        |                                                                                                      |  |  |  |  |  |  |

|          | Generate Post-Synthesis Simulation Model                                                                   |          | 538        | architecture structural of mimo4_encode1_cw is 🗸                                                     |  |  |  |  |  |  |

|          | Constant Design     Generate Programming File                                                              |          | •          | •                                                                                                    |  |  |  |  |  |  |

| ISE      | Start 🕫 Design 👘 Files 📭 Libraries                                                                         | ISE      | ISE Design | ı Suite InfoCenter 🗵 🗵 Design Summary 🗵 📄 mimo4_encode1_cw.vhd 🗵                                     |  |  |  |  |  |  |

| _        |                                                                                                            |          |            |                                                                                                      |  |  |  |  |  |  |

Fig 5.3 VHDL Code Generation

Fig 5.5 Simulation of complete 4 X4 MIMO-OFDM model in ModelSim

### 5.3 Variations in Data rates

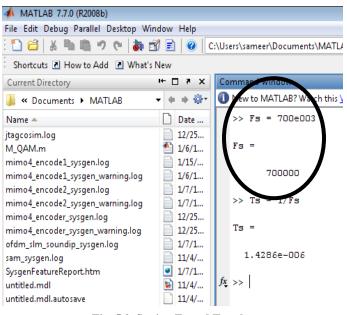

In order to change the data rate Fs and Ts values is to be set. Fs and Ts are the sampling frequency and sample period at the input which appears at the Matlab Workspace as shown in figure 5.6.

| Workspace  | rkspace          |         |        |  |  |  |

|------------|------------------|---------|--------|--|--|--|

| 1 🖬 🐿 🛍 🗞  | VV - Stack: Base | -       | ]      |  |  |  |

| Nama 📥     | Value            | Min     | Max    |  |  |  |

| 🕂 Fs       | 4000             | 4000    | 4000   |  |  |  |

| H Ts       | 2.5000e-04       | 2.5000  | 2.5000 |  |  |  |

|            | 1                | 1       | 1      |  |  |  |

| Η ber1     | <500x3 double>   | 0.4875  | 4497   |  |  |  |

| 🖶 in       | <4000x1 double>  | -0.5251 | 0.1141 |  |  |  |

| 🔁 ip_sound | <1x1 struct>     |         |        |  |  |  |

| Η simout   | <563x1 double>   | NaN     | NaN    |  |  |  |

| Η temp     | <4000x1 double>  | 60.7852 | 142.60 |  |  |  |

| 🛨 tout     | <1000x1 double>  | 2.2417  | 2.2500 |  |  |  |

Fig. 5.6 Fs and Ts values in Matlab Workspace

At the input, by default the sampling frequency is 4 K Hz and Sample

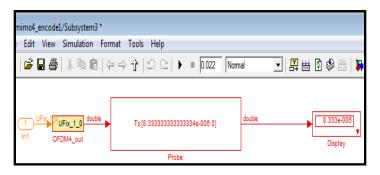

period is Ts = 1/Fs. The data rate at the transmitter can be seen with the help of sample time block as shown in figure 5.7.

The sample time at the transmitter as shown in figure 5.8 Ts = 8.33333334e-006. The sampling frequency at the transmitter is Fs = 1/Ts = 1/8.33334e-006 = 0.1 MHz i.e. 0.1Mbps. To change the Sampling frequency at the transmitter to 21 MHz, Fs = 700 KHz is to be set in the Matlab workspace and run the model as shown in figure 5.9.

Fig. 5.8. Ts display on probe in Sample Time Block

Fig. 5.7. Sample Time Block

Fig. 5.9. Setting Fs and Ts values

The transmitter data rate can be probed by sample time block where Ts = 4.762e-008, Fs = 1/Ts = 1/4.762e-008 = 21e006 = 21 MHz so, the data rate becomes 21Mbps. Similarly Fs can be changed to various frequencies and data rate can be achieved to 54 \*4 = 216 Mbps. The list of Input sampling frequencies to change transmitter sampling frequencies and achieved data rates between 84 to 216 Mbps are as shown below.

| ~   |                |                        |              |  |

|-----|----------------|------------------------|--------------|--|

| Sr. | Input Sampling | Transmitter Sampling   | Data Rate of |  |

| No. | Freq.          | Freq.(i.e data rate of | four streams |  |

|     |                | single stream)         | (4 X 4 MIMO) |  |

| 1   | 700 KHz        | 21 MHz                 | 84 Mbps      |  |

| 2   | 840 KHz        | 25 MHz                 | 100 Mbps     |  |

| 3   | 980 KHz        | 29 MHz                 | 116 Mbps     |  |

| 4   | 1.120 MHz      | 33 MHz                 | 132 Mbps     |  |

| 5   | 1.3 MHz        | 39 MHz                 | 156 Mbps     |  |

| 6   | 1.5 MHz        | 45 MHz                 | 135 Mbps     |  |

| 7   | 1.7 MHz        | 51 MHz                 | 204 Mbps     |  |

| 8   | 1.8 MHz        | 54 MHz                 | 216 Mbps     |  |

Fig.5.10. Changed Ts value in probe of Sample Time Block

#### 6. CONCLUSION

The paper resulted in designing a real time spatially multiplexed 4 x 4 MIMO OFDM transceiver using 16 QAM and implementing it on Spartan Vitex-6 FPGA board with help of Matlab Simulink, Xilinx and System Generator. Thus MIMO transmits four data streams through a single channel, thereby can deliver four or more times the data rate per channel without additional bandwidth or transmit power. Data rate up to 216 Mbps is achieved. Test benches for individual model were developed and tested it for its correct functionality and finally all the blocks were mapped together to make a complete model. The hardware co-simulation, RTL Schematics, Test Bench and VHDL codes, are also obtained for the implemented 4 X 4 MIMO OFDM model to verify its correct functionality.

#### ACKNOWLEDGEMENT

Our thanks to the experts who have contributed towards development of the MIMO OFDM

#### REFERENCES

- R.Deepa, Iswarya S, G.DivyaShri, P. MahathiKeshav, P.JaganyaVasan, and SenthilMurugan.S "Performance of Possible Combinations of Detection Schemes with V-BLAST for MIMO OFDM Systems," in IEEE pp. 140-144. 978-1-4244-8679-3/11. Coimbatore, India. 2011.

- [2] K. C. Chang and Gerald E. Sobelman "FPGA Based Design of a Pulsed-OFDM system," IEEE APCCAS, 2006, pp. 1128-1131

- [3] T. E. V. Vamsee Krishna and G TejaRavishankar "Enhancing MIMO features for OFDM," in IEEE 978-1-4244 6589-7/10, ICCCN 2010

- [4] K. C. Chang and Gerald E. Sobelman "FPGA Based Design of a Pulsed-OFDM system," IEEE APCCAS, 2006, pp. 1128-1131.

- [5] SalwaSeragEldin, Mohamed Nasr, Salah Khamees, EssamSourour, and Mohamed Elbanna "LDPC coded MIMO OFDM-Based IEEE 802.11n Wireless LAN," in IEEE 978-1-4244-3474-9/09, Egypt, 2009.

- [6] SimonHaene, David Perels and Andreas Burg "A Real Time 4-Stream MIMO-OFDM Transceiver: System Design, FPGA Implementation, and Characterization," in IEEE Jour. Vol 26, No 6, pp. 877-889, 2008.

- [7] ZohaPajoudi and SiedHamidrezaJamali "Hardware Implementation of a 802.11n MIMO OFDM Transceiver", International Symposium on Telecommunications, 2008, pp. 414-419

- [8] Yu Wei Lin and Chen Yi Lin, "Design of FFT/IFFT Processor for MIMO OFDM Systems", IEEE Transaction on circuit and system, vol. 54, no. 4, pp. 807-815, 2007

- [9] V. Tarokh, et. al., "Space-time block coding for wireless communications: performance results," IEEE Jour. On Sel. Areas in Commun, vol. 17, no. 3, pp. 451-460, 1999.

- [10] Chetty Garuda, Mohammed Ismail, "A Multi-Standard OFDM-MIMO Transceiver for WLAN Applications," in IEEE pp. 1613-1616, Columbus, OH, USA, 2005.

- [11] Hujun Yin and Sivash Alamouti, "OFDMA: A Broadband wireless Access Technology," Intel Corporation, 2008

- [12] Angela Doufexi, Arantxa Prado Miguelez, Simon Armour, Andrew Nix, and Mark Beach "Use of Space Time Block Codes and Spatial Multiplexing using TDLS Channel Estimation to Enhance the Throughput of OFDM based WLANs," University of Bristol, UK, 2003, p.p.704-708.

- [13] D. Getsberg, Da-shanShiu, Peter J. Smith, and AymanNaguib "From theory to practice: An overview of MIMO space-time coded wireless systems," in IEEE Journal in Selected Areas On Communication, vol. 21, no. 38, pp. 281-301, 2003.

- [14] Wikipedia, "MIMO", http://en.wikipedia.org/wiki/MIMO

- [15] Xilinx, "System Generator for DSP, User Guide", http://www.xilinx.com/support/documentation/sw\_manuals/xili nx14\_1/sysgen\_user.pdf

- [16] MathuranAthan "Simulation of OFDM system in Matlab BER VsEb/N0 for OFDM in AWGN channel" Gaussian Waves, http://www.gaussianwaves.com/2011/07/simulation-of-ofdmsystem-in-matlab-ber-vs-ebn0-for-ofdm-in-awgn-channel.

# **IJSER**