# The Design of Ring VCO by using clock gating in 130 nm CMOS

Priya Yadav M.Tech Scholar <u>priyadav9413@gmail.com</u> Suresh Gyan Vihar University

Abstract- A genuine modulator constituted on QPSK modulator that is ployed for the confinement of the injection in the modulation of phase along the formulation of clock that is locked in phase. As per the suggested gating of clock & a VCO, optimization of absorption of power & delay is performed. A CMOS of 130nm is formulated by the recommended modulator of QPSK. The delay of 3.63ns is attained & the power that is used is 5.931240e-009W.

*Index Terms*—CMOS, injection locking, modulator, quadrature phase-shift keying (QPSK), ring voltage-controlled oscillator (VCO).

#### **1. INTRODUCTION**

An oscillator of ring is comprised of an odd number comprised of logical gates of NOT where outcomes oscillates in between the two states of voltage termed as false & true. The logical gates of NOT are linked to each other in a chain & then the outcome generated by the last inverter is provided to the commencing one.[1]

As a logical NOT is determined by the input of the inverter, it is placid that the extreme outcome in the chain the figures are NOT in logics of the commencing input. The last outcome generated retains a fine time after the invasion of commencing inputs providing the feedback of the extreme outcome to the input that produces oscillations.

An oscillator of ring can't be deployed in a chain of circles of inverters which are even in quantity. The commencing input & extreme outcome both are equal in this scenario. Though this schema is used to retain the data & is the main constituents of SRAM.

The state of an oscillator of ring is more protected to the noises of the surrounding. The renders are not inverting. By the amalgamation of non inverting & inverting states, a ring oscillator can be formulated in a condition where the sates of inversion are odd. The adding up of distinct states formulates the period of oscillations.[2]

Mr. Ghanshyam Jangid Asst.Professor Dept. E&C jangidghanshyam85@gmail.com Suresh Gyan Vihar University

Only power is needed for the oscillations by an oscillator of ring. The commencement of oscillations become spontaneous as the limit of voltage of threshold is attained.

There are mainly two methodologies employed to rise the frequency of the oscillations. First step is to raise the voltage that is implied. This enhances the absorption of current & frequency. The extreme voltage that can be implied is the speed. The other option is to formulate a ring from several constituted oscillators of ring at a definite consumption of power.

For the production of local signals in RF, injection locking is the most used methodology. As the locking of injection possess a superiority being the simplest topology & deduce the noise. Parallel there are several documents that are associated to the modulation/demodulation of phase constituted on the shift of the phase.[3]

A genuine modulator constituted on QPSK modulator that is constituted on a VCO. By making use of injection of pulse, noise in phase is minimized by attaining the modulation of phase in QPSK.

# II. QPSK MODULATOR WITH DIRECT INJECTION-LOCKED

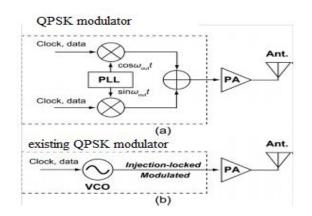

Figure reveals the traditional QPSK constituted on a Q-OPLL which ploys several segments of RF like DACs & mixers & filters. As the result, much area is taken into account & power is produced with mixing.[1]

Figure :- 1(a) QPSK modulator (b) Existing direct injection-locked QPSK modulator.

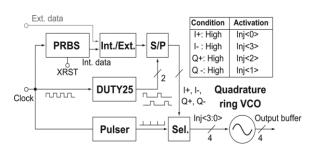

The clocks of the phase locks were formulated in the locking of injection on a ring of VCO. The modulation in phase was attained in many other segments like PA & PM. Eventually the modulation in phase was attained by regulation the frequency which is in resonance of VCO considering the locking of phase with injections & swap circuit polarity. The modulator of QPSK as suggested which makes use of attributes of locking of injection like locking of phase & mixing. Modulation & locking of phase are attained simultaneously by using the synchronized information with clock. The smaller & uncomplicated can be attained as the modulator of QPSK makes use of a VCO ring & injection of pulse in the modulation of phase. The figure no. 2 reveals the modulator of OPSK.[6] It is comprised of a quarter formulator of pulse by the clock, selector of data either external or internal, S/P circuitry, PRBS. The data formulated by the PRBS is applied for the computation on the high state of XRST. The blocks as described have the ability to demultiplex the S/P sequencing. It is comprised of pulsar, selector & VCO. The pulses of injection are chosen by the selector in the sequence (I+,I-,Q=,Q-). [5] By the outcome, the pulses of input in the modulation of phase are deployed in the VCO.

Figure 2. Diagram of modulator of QPSK.

The signal which is invaded to each Q & I-phase in the delay cell as of the format of rail pulses locking of injection in sub harmonic manner, which are formulated by the pulsar constituted on NAND. The width of pulse can be regulated by the pulsar & the pulses produced are lesser than 100ps. In the suggested VCO of ring, the switching is done in the nMOS between the ground & out produced node as the differential outcomes are implemented.

The pulses to be injected are provided to I & Q-Phase outcomes. The latch of nMOS is comprised in the delay cells by feedback to accumulate the condition of oscillation.[1] The latch can retain the oscillations with the injection of pulses of I/O.[1] To tune the outcome of frequency that is oscillated, the loads of pMOS resistance should be deployed. There are 8 cells in the MOS.

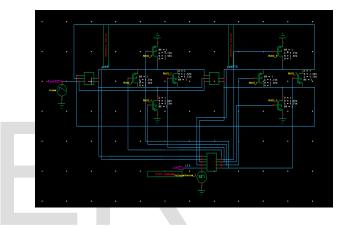

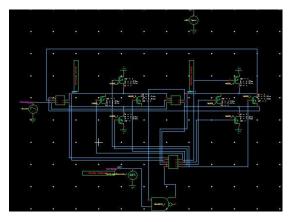

Figure 3:-Two-stage differential ring VCO by tanner

It visualizes the waveforms of clock of input, parallel sequence of data, INJs, outcomes of VCOs. Where it is assumed that outcome of VCO is integral multiple of frequency of clock. The commencing state is the locking state Firstly, supposed that the initial state is the state locking of INJ. It is considered by the injection of timings & imbalancement in phase of the outcomes of the oscillator when the pulses of short length are relayed.

#### 2. SUGGESTED METHODLOGY

In order to make the dissolution of power minimal in circuits lying in their synchronous state, gating of clocks is one of best approach considered so far. In order to prune the tree of clocks, more logics are implemented in the circuit by gating of clocks which intend to save the power. The removal of clocks from the circuit deactivates some sections of the circuit thus not allowing them to switch in the different states. The states that vary continuously absorb extra power. The absorption of power becomes almost negligible when no switching of states occurs & thus the current indulged from the leakage are induced in it goes to zero, and only leakage currents are incurred.

The condition of gating of clocks makes use of situations activated to join the registers in & thus do clock gating. So in order to make the best use of gating of clocks & gain some advantage from it, it is highly recommended to invade these conditions of activations in the design. As a large quant of muxes are eliminated & replaced by the logics applied by gating of clocks, this process also preserves the power & die area.[7]

The standard representation of logics formulated by gating of clocks is ICG ie. Cohesive gating of clock, But since the logics will be retained in the form of a tree of clocks these logics may make some significant variations in the design of tree of clocks.

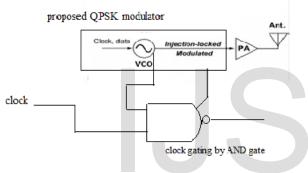

Figure 4:- Proposed QPSK modulator with clock gating

There are numerous ways to implement the logics of gating of clocks in the design:

- 1. Embedded into the code of RTL as by the activation policies that may be transformed by themselves into logic of gating of clocks by tools that are synthesized.

- 2. The designers of RTL invade the design by their own by invading the library specified as ICG cells that gate the clocks of particular registers.

- 3. By the automatic tools for gating of clocks, semi automaticity is invaded in the RTL. Either cells of ICG are invaded in to RTL or conditions for the activation are embedded into the code of RTL. This eventually provides optimization of gating of clock in a sequential manner.

Note: the re-evaluation of the variations of functions is needed to be done as there are variegated values accumulated in the registers, as an outcome by the intention of manipulations done in RTL for improvisation of gating in clocks.

The process to withdraw the conditions of activation to the elements of downward or upward stream in a sequential manner is termed as gating of clocks in a sequential manner & thus the extra registers can be gated by clock.

So, as per the explanation, the circuits which are asynchronous don't possess a clock. To express the reaction of circuit of asynchronous state that are constituted on the basic probabilities on the dependence of data, this term is described the absolute gating of clocks. By the time the granularity attains zero value, on which the circuit in synchronous state is gated on, the absorption of power becomes equivalent to a circuit in asynchronous circuit. The logical transactions are produced only when the computations are performed actively.

The community of chips like OMAP3 accumulated with mobile phone assists variegated types of gating of clock. On one side gating of clocks can also be done manually by making use of driver software that activates or deactivates the clocks required by a controller retained at a neutral state, while on the other side the gating of clocks can also be performed automatically in which the hardware itself analyze the usage of clock & turn it off when it is not in use.[8]These types of forms can communicate with each other & may become the part of a same segment. As an illustration the internal bus may use automated form of gating & thus it is made as off gate still it is required by DMA or CPU or else various accessories.

The main purpose of gating of clocks is to improvise the throughput of the system.

Figure 5:- VCO of Ring by tanner along the Clock Gating By And Gate

## 3. RESULTS

## 3.1 Existing Design

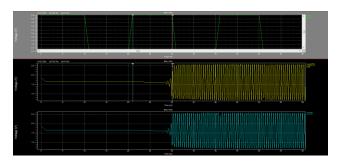

Figure 6:- Output waveform for existing design

The waveform of outcome is of the frequency OUT270 & OUT0.

Delay :- 9.10ns

Average power consumed -> 1.580999e-008 watts

## 3.2 Proposed Design

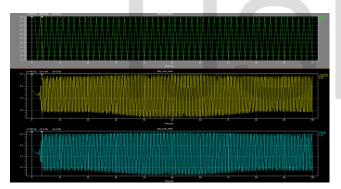

Figure 7:- Output waveform for proposed design

The waveform of outcome is of the frequency OUT270 & OUT0.

Delay :- 3.63ns

Average power consumed -> 5.931240e-009 watts.

#### Table 1:- Comparison of the Proposed design parameter

|              | Delay | Technology<br>(nm) | Supply<br>Voltage<br>(V) | Power<br>(mW) | Modulation     |

|--------------|-------|--------------------|--------------------------|---------------|----------------|

| 2012         | 6.52  | 65                 | 1                        | 0.938         | 8PSK<br>O-QPSK |

| 2012         | 8.78  | 180                | 1.8                      | 5.88          | QPSK<br>O-QPSK |

| 2014         | 9.10  | 180                | 1.8                      | 0.00158       | QPSK           |

| This<br>work | 3.63  | 130                | 1.3                      | 0.000593      | QPSK           |

## CONCLUSION

A straight modulator of QPSK is suggested with the locked injection by making use of gating of clocks in the traditional structure of PLL. Here the locking of injection was deployed for the modulation of phase as well its locking. By removing the inductor & additional segments of PLL, a simple & scaled modulator of QPSK is attained. The power & delay are being improvised with respect to the present design.

## REFERENCES

[1]Sang Yeop Lee, Noboru Ishihara, "A Novel Direct Injection Locked QPSK Modulator Based on Ring VCO in 180 nm CMOS" *IEEE Microwave and wireless components letters*, VOL.24, NO.4 April 2014.

[2] M. M. Izad and C. Heng, "A 17 pJ/bit 915 MHz 8PSK/O-QPSK transmitter for high data rate biomedical applications," in *IEEE CICC Dig.*, Sep. 2012, pp. 1–4.

[3] S. Diao, Y. Zheng, Y. Gao, S. Cheng, X. Yuan, M. Je, and C. Heng, "A 50-Mb/s CMOS QPSK/O-QPSK transmitter employing injection locking for direct modulation," *IEEE Trans. Microw. Theory Tech.*, vol. 60, no. 1, pp. 120–130, Jan. 2012.

[4] J. Bae, K. Song, H. Lee, H. Cho, and H.-J. Yoo, "A low-energy crystal- Less double-FSK sensor node transceiver for wireless body-area network," *IEEE J. Solid-State Circuits*, vol. 46, no. 2, pp. 416–423, Feb. 2011.

International Journal of Scientific & Engineering Research, Volume 6, Issue 10, October-2015 ISSN 2229-5518

[5] Q. Zhu and Y. Xu, "A 228 m 750 MHz BPSK demodulator based on injection locking," *IEEE J. Solid-State Circuits*, vol. 46, no. 2, pp. 416–423, Feb. 2011.

[6] B. Razavi, *RF Microelectronics*. Upper Saddle River, NJ, USA: Prentice-Hall, 1998.

[7] https://en.wikipedia.org/wiki/Clock gating.

[8] Himanshu Chaudhary, Nitish Goyal, Nagendra Sah "Dynamic Power Reduction Using Clock Gating" IJECT Vol. 6, Issue 1, Jan - March 2015

# IJSER

5