# Minimization of Leakage Current in VLSI Design

Kanika Kaur, Arti Noor

Abstract - To meet the ever-increasing demand of high performance systems, more and more functions are integrated into single chip by scaling down the size of device. Leakage current is becoming an increasingly important fraction of total power dissipation of integrated circuits. As technology scales leakage current grows exponentially and become and increasingly large component of total power dissipation. An important area of research is developing the circuit techniques to reduce the subthreshold leakage current in both active and standby mode to minimize the total power consumption. The power dissipation due to subthreshold leakage current becomes comparable to switching or dynamic power component and is a serious concern for circuit designing in deep submicron region. This paper describes the need to consider gate leakage current while determining the sleep state pattern is explained. Circuit reorganization and sleep state assignment techniques demonstrated for gate and subthreshold minimization of static and dynamic circuits. The MTCMOS technology for the minimization of gate and subthreshold leakage current is also explained for the low power circuits.

Index Terms: - Gate Leakage, Subthreshold leakage Current, Static circuits, Dynamic circuits, MTCMOS, CMOS

## I. INTRODUCTION

In the past, the figure of merits for VLSI Design was high speed, low cost and small area without much bothering about power dissipation but in present scenario demand of low power design is addressed. In recent years, the aggressive scaling of device dimensions and threshold voltage have significantly increased sub-threshold leakage and its contribution to the total chip power consumption. Also, gate oxide thickness has been scaled to maintain adequate control of the channel by the gate. This has resulted in an alarming increase of late in gate leakage current due to tunneling through the thin gate oxide. Gate leakage is expected to be a major component of leakage in future technology generations and has been identified as one of the most important challenges to future device scaling [1]. Gate leakage power, which was almost non-existent in the previous technology generations, is expected to contribute more than 15% to the total chip power dissipation in the today's technology generations. To date, most circuit-level leakage minimization techniques focus only on sub-threshold leakage reduction, without considering the effects of gate leakage. Gate leakage is primarily being addressed from a CMOS technology perspective and the use of high-k gate dielectrics have being proposed. One of the approaches that addresses gate leakage, BGMOS [2], uses multiple threshold voltages and multiple oxide thickness devices. The use of PMOS dominated circuits was proposed in [3], on the basis that PMOS devices exhibit lower gate leakage compared to identical NMOS devices. However, due to band-to-band tunneling and use of different dielectrics [4], the gate leakage through PMOS devices is no longer negligible and needs to be considered. In this paper, we account for the contribution of gate leakage on total leakage by considering forward and reverse gate tunneling through both NMOS and PMOS devices. Gate leakage in conventional sleepstate patterns (which focus only on sub-threshold leakage) are evaluated and new sleep-state assignments for transistor stacks are proposed for total leakage minimization. We also present circuit re-organization schemes for total leakage reduction of dynamic circuits in sleep mode. Finally, we look into the effect of gate leakage on the MTCMOS circuit scheme and propose the use of sleep-state assignment in conjunction with MTCMOS to obtain increased total leakage savings.

## II. GATE LEAKAGE ANALYSIS

Gate leakage current for an NMOS transistor of 0.1m process shows an exponential dependence on the gate-to-source bias. At high gate bias, gate leakage current decreases with increasing drain-to-source bias. This can be attributed to the fact that a higher drain voltage results in a smaller electric field across the gate oxide at the drain end of the channel (lower VGD). At low gate bias, gate leakage was found to increase with increasing drain bias (due to the increase in reverse gate leakage with increasing drain bias, i.e., VGD). Thus, for a given gate-to-source bias, gate leakage is minimum when the gate-todrain voltage is minimized. In addition, gate leakage current was found to be almost insensitive to the body-node voltage. The techniques presented in subsequent sections aim at minimizing the gate-to-source (VGS) and gate-to-drain (VGD) bias across a majority of devices, thereby obtaining a reduction in gate leakage and total leakage of the circuit.

## **III. STATIC CIRCUITS**

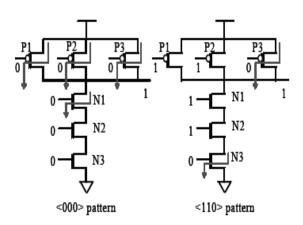

Consider a three-high NMOS transistor stack (as found in the Nand3 cell shown in Fig. 1). The sub-threshold leakage

through the transistor stack is minimized when all of the devices in the stack are turned 'OFF', i.e., when a <000> pattern is applied. Since conventional leakage minimization techniques focus on sub-threshold leakage, the <000> pattern is believed to be the lowest leakage vector for a Nand3 cell. However, when such a pattern is applied, the output is high, and all of the PMOS devices experience high gate-to-drain and gate-to-source voltages. This results in a high field across the gate oxide causing gate leakage, which can be substantial due to the greater width of PMOS devices. To reduce gate leakage, it is necessary to

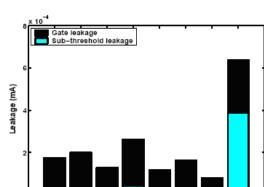

maintain the terminals of most of the devices at the same potential. This can be achieved by turning 'ON' all but the lowest NMOS transistor in the stack, i.e., by applying the input pattern <110>. Under such an input vector, only one PMOS device (P3) exhibits gate leakage. The gate leakage of the 'ON' NMOS transistors (N1, N2) is also negligible, since the internal nodes in the stack are charged almost to the supply rail (and hence the devices have a low VGS/VGD). The 'OFF' transistor (N3) at the bottom of the stack prevents subthreshold leakage from increasing tremendously. The total leakage for some of these vectors (fig-2) is clearly dominated by the gate leakage component. Even though sub-threshold leakage for the vector <110> is greater than sub-threshold leakage for the vector <000>, <110> is the minimum total leakage state for Nand3 cell. Thus, it is necessary to re-evaluate conventional leakage minimization schemes and input vector assignments to account for the effect of gate leakage. With gate leakage expected to increase more rapidly than sub-threshold leakage, we expect that turning 'ON' all but the lowest device in a transistor stack will be the lowest leakage state for a transistor stack in future technology generations.

Fig.1 Input patterns for NAND3 cell

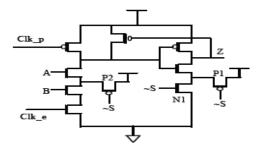

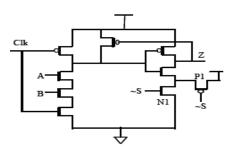

#### **IV. DYNAMIC CIRCUITS**

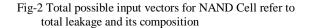

This section focuses on sleep-state leakage minimization of dynamic circuits. Consider a typical 2-input dynamic AND cell as shown in Fig.3 During sleep state, the clock is held either in the precharge phase (low) or the evaluate phase (high). If the clock is held in the evaluate phase, the dynamic node will be discharged, and the output will be at logic high. Since, in a domino chain, the output of a dynamic cell drives other similar cells, it can be assumed that the inputs to the dynamic cell will also be at logic high. In such a state, all of the devices in the pulldown n-stack and the output pull-up transistor (i.e., devices on the evaluate path) will exhibit gate leakage. Since these devices are sized to reduce delay, it can result in significant gate leakage current. The sub-threshold leakage in this state is small, since it is primarily through the devices on the precharge path. On the other hand, when the clock is held in the precharge phase, the dynamic node is charged high, the output will be at logic low and the inputs can be assumed to be at logic low. In this case, the devices on the precharge path exhibit gate leakage, while the devices on the evaluate path contribute to the sub-threshold leakage. Though sub-threshold leakage of the NMOS pull-down tree is minimal due to stacking effect, sub-threshold leakage through the wide output pull-up transistor can be considerable. Thus, in either of the two states, the total leakage of the cell may be high, although due to different mechanisms. Conventional techniques claim that holding the clock in the evaluate phase is the lowest leakage sleep state, but this approach completely neglects gate leakage. Two proposed schemes are shown in Fig. 4. Both of these aim to minimize the total (sub-threshold plus gate) leakage current of the cell in sleep state. The output pulldown tree is modified to incorporate two small devices (N1, P1) that are controlled by the sleep-state control signal S. The precharge and evaluate clocks are separated in Scheme A. This will need additional circuitry for clock separation and can also result in clock skew problems. Scheme B uses a single clock, similar to the original configuration. In Scheme A, in sleep state, the precharge clock is held high, while theevaluate clock is held low. The inputs to the cell can also be assumed to be high. The activated conditional pull-up devices (P1, P2) therefore charge the dynamic node and the output to logic high. In this state, gate leakage of both the evaluate and the precharge paths are reduced (only the evaluate transistor exhibits reverse gate leakage

IJSER © 2012 http://www.ijser.org current) since most of the devices see an identical voltage at all of their terminals. The sub-threshold leakage of the output pull-up PMOS device is also reduced due to the 'OFF' device N1, resulting in significant savings in total leakage power. Since all of the additional devices are small, the delay degradation on the critical path is minimal. The additional devices can be desirably sized to obtain requisite precharge times and leakage savings. For Scheme B, the clock is held low in sleep state. The dynamic node and the output of the cell are high (similar to scheme A) reducing the gate and sub-threshold leakage of the output PMOS inverter. The savings in total leakage is slightly reduced, since the precharge transistor exhibits gate leakage in addition to an increase in the sub-threshold leakage through the evaluate tree. However, in this configuration, no additional devices are needed in the evaluate tree, minimizing the delay degradation. The percentage savings obtained in gate leakage power and total power, along with the area overhead and degradation in precharge and evaluate times, are listed in Table 1 for several commonly-used dynamic circuits. For instance, savings of over 73% in gate leakage and 13% in total leakage are obtained for the dynamic AND cell shown in Fig. 3,4,5 by using Scheme A with an area penalty of less than 7% and just over 1% degradation in delay. Fig 3,4 & 5 describe for Dynamic circuit reorganization for gate and total leakage minimization.

Fig-3 Typical two Input AND Gate

Fig-4 Scheme A, Separate Precharge and Evaluate logic

Fig-5 Scheme B, Single Precharge and Evaluate logic

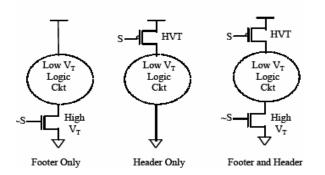

### V. MTCMOS CIRCUITS

The MTCMOS scheme has been proposed for reduction of subthreshold leakage current in sleep state [5]. In thissection, we investigate the effect of the MTCMOS configuration on gate and total leakage. The three configurations shown in Fig. 5 are considered. In the sleep state, the high VT footer and header devices areare turned 'OFF' (thereby minimizing sub-threshold leakage current). This causes the virtual supply rails to be close to VDD or ground (if only footers or headers are used), or to be close to VDD/2 (if both headers and footers are used). The total leakage is the sum of the sub-threshold leakage of the sleep devices, the gate leakage of the sleep devices and the gate leakage of the input stage. The devices of the first stage may exhibit gate leakage depending on the input vector. For instance, if only footers are used, the virtual ground plane will be close to VDD. Thus, all of the devices in the logic circuit have their drain and source at nearly the supply rail. If an input vector of <0000> is applied, then all of the devices in the first stage will see a high VGS and VGD, and hence exhibit gate leakage. However, when an input vector <1111.> is applied, these devices will have identical voltage at all of their terminals, resulting in minimal gate leakage. This makes the leakage in sleep-state for the footer-only, configuration dependent upon the applied input vector.

A similar argument can be presented for the header only configuration. Here if Header only or footer only scheme is used, an appropriate input vector (00000... or11111....) should be applied to obtain maximum savings in total leakage This is validated in Fig. 6 which plots the gate leakage for an industry-standard decode circuit for each of the above schemes. In this case, the first 23 vectors are randomly generated, while vectors 24 and 25 are the <000...> and <111...> vectors. Here the total leakage for the header only configuration with the <000...> input vector is over 50% lower than the average leakage of remaining 24 vectors. Similarly, the application of the <111...> vector for the footer only configuration results in over 40% savings compared to the average leakage of the sleep-state devices

(headers and footers) can be significant since these devices experienced a high reverseVGS and VGD. leakage can be reduced by using both headers and footers. When both headers and footers are used, the virtual supply and ground rails float close to VDD/2. The gate-to-drain and gate-to-source bias across the sleep devices is reduced by about half, and hence their gate leakages are reduced. The gate leakage of the input stage is also reduced. Table 2 lists the ratio of the leakage currents for the MTMOS configurations of Fig. 6 compared to the leakage of the original circuit for an industry standard decode circuit in an advanced process.

Fig-6 MTCMOS configuration (A, B, &C) evaluated

|                    | Subthreshold<br>savings | Gate<br>leakage<br>Savings | Total<br>leakage<br>savings |  |

|--------------------|-------------------------|----------------------------|-----------------------------|--|

| Footer Only        | 15.1                    | 39.6                       | 80.8                        |  |

| Header<br>Only     | 111.0                   | 28.4                       | 61.2                        |  |

| Header &<br>Footer | 720.3                   | 270.1                      | 505.3                       |  |

Table 2: Leakage currents ratio for MTCMOS configurations of

Fig. 6 compared to original circuit

# **VI. CONCLUSIONS**

In this paper we have shown the growing importance of gate leakage current and have clearly demonstrated the need to consider gate leakage in any leakage minimization scheme. We provided an analysis of gate leakage and presented optimal sleep-state assignments for transistor stacks in static circuits. We proposed new dynamic circuit

The savings in total leakage current using these schemes range from 2% to 38% with less than 7% increase in device area. Also try to evaluate the MTCMOS from a gate leakage perspective and illustrated the need to use both headers and footers to obtain maximum leakage savings.

# 7. REFERENCES

International Technology Roadmap for Semiconductors,

International Technology Roadmap for Semiconductors,

Edition, *http://public.itrs.net/Files/20011TRS/Home.html* T. Inukai, et.al, "Boosted Gate MOS (BGMOS): Device/

Circuit Cooperation Scheme to Achieve Leakage-Free Giga-Scale Integration," *Proc. CICC 2000*, pp.409-412

F.Hamzaoglu and M. Stan, "Circuit-Level Techniques to

Control Gate Leakage for sub-100nm CMOS," *Proc. ISLPED*,

pp. 60-63, Aug. 2002.

[4] Y. Yeo, et.al, "Direct Tunneling Gate Leakage Current in Transistors with Ultrathin Silicon Nitride Gate Dielectric," *IEEE Electron Devices Letters*, vol.21, no.11, pp. 540-542, Nov. 2000.

[5] S. Mutoh, et.al, "1-V Power Supply High-Speed Digital Circuit Technology with Multi-Threshold Voltage CMOS," *IEEE Journal of Solid State Circuits*, vol. 30, no. 8, pp. 847-854, Dec2003.

#### About author

Kanika Kaur (Associate Professor, KIIT, Gurgaon) received B.Sc (Electronics) Hons. Degree from Delhi University in 1997 and M.Sc (Electronics) Hons. Degree from Jamia Millia Islamia University in 1999.She received M.Tech degree from RTU in 2005 and presently pursuing Ph.D from the JJTU, Rajasthan in the field of "Low power VLSI designsubthreshold leakage reduction technique for CMOS". Published more than 20 research papers in national, international journal & conferences. She has also published a book titled "Digital System Design" by SciTech Publication in 2009. Editor of 05 Technical Proceedings of National & International Seminars. Convener of many National and International Symposium. Life member of IETE & ISTE. Awarded as best academic personality& HOD in 2007 and 2008 at NIEC, Delhi.

Table 1: Percentage savings and penalties for dynamic circuit reorganization schemes of fig.3, 4, & 5 compared to conventional dynamic circuit

| Circuit      | Scheme A                   |                            |                     |                      |                 | Scheme B                   |                            |                     |                      |                     |

|--------------|----------------------------|----------------------------|---------------------|----------------------|-----------------|----------------------------|----------------------------|---------------------|----------------------|---------------------|

|              | Gate<br>leakage<br>savings | Total<br>Leakage<br>saving | Evaluate<br>Penalty | Precharge<br>penalty | Area<br>penalty | Gate<br>leakage<br>savings | Total<br>Leakage<br>saving | Evaluate<br>Penalty | Precharge<br>penalty | Area<br>penalt<br>y |

| 3 i/p<br>And | 73.50                      | 13.0                       | 1.20                | 27.90                | 6.00            | 51.3                       | 14.0                       | -0.51               | 27.3                 | 4.03                |