# Low Cost Design of Sequential Reversible Counters

Shubham Gupta, Vishal Pareek, Dr. S.C.Jain

Abstract - Reversible computing has attracted the attention of researchers due to its low power consumption and less heat dissipation. A number of reversible gates have been proposed by different researchers and various combinational circuits based on reversible gates have been proposed. Sequential circuits were not available because of feedback was not allowed in reversible circuit. However allowing feedback in space (not in time), some sequential reversible gates and circuits have been reported in the literature.

In this work, we propose a novel reversible gate and low cost T flip-flop by using our proposed gate. The proposed gate has significant improvement over earlier design in terms of garbage outputs, constant inputs and number of reversible gates. The design of efficient asynchronous and synchronous reversible counters has also been proposed. We hope this work will strengthen the development in the field of reversible sequential circuit.

Index Terms - Low-power VLSI, Reversible logic, Reversible counters, Reversible flip-flop, Sequential circuits

## **1 INTRODUCTION**

WITH increasing complexity of digital circuits, the heat dissipation is becoming a major issue to continue growth momentum. In early 1960's R. Landauer [1] showed that reversible hardware computation results in energy dissipation because of information loss. It has been proved that each bit of lost information will lead to dissipation of at least KTln2 joule of energy, where K=1.3806505 x  $10^{-23}$  m<sup>2</sup>kg<sup>-2</sup>K<sup>-1</sup> is the Boltzmann's constant and T is the absolute temperature at which computation is performed [2],[4].

It is well known that irreversible gate erase at least one bit of information in every operation. Hence these gates will always produce some heat energy. C.H. Bennet [3], [4] proved that KTln2 joule of energy would not be dissipated if the computation is carried out by a reversible gates. The applications of reversible logic are quantum computation, optical computing, ultra low power CMOS design, DNA computing and nanotechnology etc.

In 1980, Toffoli [5] has proposed a well known Toffoli Gate and other reversible gates followed by Fredkin Gate [7] in year 1982 that has begun an era of reversible computing. Since then the development of reversible circuits is growing as an alternative of conventional irreversible computing. In reversible circuits feedback & fan-out are not allowed [8] and number of inputs and outputs must be equal. Like irreversible computing, the work is in progress of reversible computing for development of various circuits representation formats, hardware description languages, circuit synthesis and optimization algorithms, fault tolerance and design of sequential circuits etc.

Reversible circuit representation format like Reed-Muller expansion, PPRM etc. explained by Mehdi Saeedi and Igor L. Markov [9]. Syrec language for reversible hardware description was proposed by Robert Wille et al. [10]. Circuit synthesis and optimization algorithms such as Transformation-based methods [11], Search-based methods [12], Cycle-based methods [13] and BDD [14] were proposed by different researchers. In order to incorporate fault tolerance in reversible circuits a number of fault tolerant techniques and synthesis have been reported [15]. Anugrah Jain et al. [16] have exploited the parity preserving fault tolerance characteristics of PPTG Gate in year 2013.

Due to limitation of feedback and fan-out in reversible computing, the development of sequential circuits has not been significant. Recently, A. Banerjee et al. [17] have redefined that feedback in space is allowed but not in time. Hence, the development of reversible sequential circuits has begun.

In year 2005, H. Thapiyal et al. [18] have constructed T flip-flop using basic reversible gates. SKS Hari et al. [19] have improved this design of reversible T flip-flop in year 2006. In 2008, Min-Lun Chuang et al. [21] have reported T flip-flop by using D and T latches, which an improvement design over the one proposed by H. Thapiyal [18]. In year 2010, Sayem Gate was proposed by Abu Sadat, Md. Sayem [22] and D, J-K latches were designed using Sayem Gate and basic reversible gates. In 2011, V. Rajmohan et al. [23] have proposed T flip-flop using Sayem Gate and basic reversible gates. In this work, we are proposing a new

Shubham Gupta is currently pursuing M.Tech from Rajasthan Technical University, Kota, India, E-mail id: guptashubham396@gmail.com

Vishal Pareek is currently pursuing M.Tech from Rajasthan Technical University, Kota, India, E-mail id: <u>vishalpareekrk@gmail.com</u>

Dr. S.C. Jain is currently working as a professor at Rajasthan Technical University, Kota, India, E-mail id: <u>scjain1@yahoo.com</u>

#### INTERNATIONAL JOURNAL OF SCIENTIFIC & ENGINEERING RESEARCH, VOLUME 4, ISSUE 11, NOVEMBER-2013 ISSN 2229-5518

reversible gate which will be used in the construction of T flipflop.

This paper proposes a novel concept on efficient and optimized reversible sequential circuit design of asynchronous and synchronous counters.

The next sections of this paper are as follows. Section 2 explains the basic definition of reversible logic gates and necessary reversible gates used in this work. Section 3 provides the related work in the past. Section 4 provides the details about the proposed reversible gate and T flip-flop. Section 5 provides the conventional asynchronous circuit design and its reversible design. The conventional synchronous circuit design and its reversible design have been described in section 6. Section 7 concludes the work.

## 2 BASIC DEFINITIONS OF REVERSIBLE LOGIC GATES

**2.1 Definition 1.** Reversible Gate is a circuit in which the number of outputs is equal to the number of inputs and there is a one to one correspondence between the input and output vectors [24].

**Example.** Let the input vector be  $I_V$ , output vector be  $O_V$  and they are defined as follows,  $IV = (I_i, I_{i+1}, I_{i+2} \dots I_{k-1}, I_k)$  and  $O_V = (O_i, O_{i+1}, O_{i+2} \dots O_{k-1}, O_k)$ . For each particular i, there exits the relationship  $I_V \Leftrightarrow O_V$ .

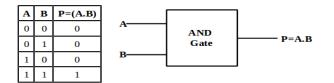

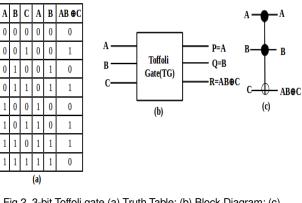

Conventional logic gates are almost all irreversible. Among the commonly used gates, only the NOT gate is reversible. The AND gate is irreversible because it violate the requirements of reversible functions as shown in Fig. 1. One way to make the AND function reversible is to add one input and two outputs as shown in Fig. 2(a). The AND function can be obtained in the third output column  $AB\oplus C$  of Fig. 2(b), when setting C = 0[5].

Fig.1. 2-bit AND gate (a) Truth Table; (b) Block Diagram

**2.2 Definition 2.** Unwanted or unused output of a reversible gate (or circuit) is known as Garbage Output.

In the reversible AND function shown in Fig. 2(a), the outputs A and B are garbage outputs which are used to make the function reversible. A set of reversible gates is needed to synthesize reversible circuits.

By using both the definitions, we can conclude that it is possible to obtain reversible logic gates and circuits from conventional irreversible gates.

Fig.2. 3-bit Toffoli gate (a) Truth Table; (b) Block Diagram; (c) Symbol

Several reversible gates have been proposed in the past. Here we introduce the Toffoli and Feynman gate, which will be used in our work.

**Toffoli Gate.** The truth table of a 3-bit Toffoli Gate (TG) is shown in Fig. 2(a), and its block diagram is shown in Fig. 2(b) [5]. The function of the third column is  $AB\oplus C$ . That means when A = B = 1, the output is inverted C; otherwise the output is C. This gate can be used to realize a 2-input reversible AND function by setting C as a constant 0 as mentioned [5].

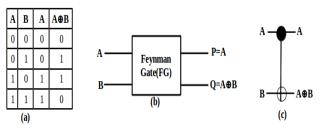

**Feynman Gate.** The truth table of a 2-bit Feynman gate is shown in Fig. 3(a), and its block diagram is shown in Fig. 3(b) [6]. Feynman Gate (FG) can be used as a copying gate. Since a

Fig.3. 2-bit Feynman gate (a) Truth Table; (b) Block Diagram ;( c) Symbol

fan-out is not allowed in reversible logic, this gate can be used for duplication of the input to two outputs.

Two restrictions on reversible logic synthesis must be followed [5]:

- i. The fan-out count of a signal net must equal one. If two copies of one signal are needed, duplication is necessary.

- A combinational reversible network has to be loop-free. It cannot contain a cyclic path.

The first restriction is in place because a fan-out structure is not reversible. For fan-out, the input signal number is one, but there are two or more output signals. Therefore, for the first restriction, we use a 2-bit Feynman Gate to duplicate a signal.

#### INTERNATIONAL JOURNAL OF SCIENTIFIC & ENGINEERING RESEARCH, VOLUME 4, ISSUE 11, NOVEMBER-2013 ISSN 2229-5518

The truth table of a 2-bit Feynman Gate and its symbol are shown in Figure 3(a) and 3(c), respectively. The function of the second output column is  $A^{\oplus}B$ . If B is set as a constant 0, a copy of input variable A will be obtained at first output P=A as well as on second output Q=  $A^{\oplus}B = A^{\oplus}0$ =A. Hence this gate enables us to obtain fan-out like duplication of n input bit [21].

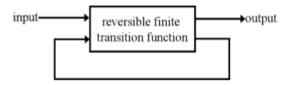

The second restriction is required because a reversible combinational function is necessarily a finite one-to-one function. It is customary to express this function in graphical form as a causality network. By construction, causality networks are "loop-free". Therefore, a combinational reversible network is loop-free [21].

These two restrictions have to be met in reversible sequential circuits as well. According to Toffoli [5], a sequential circuit is reversible if its transition function is constructed by reversible logic. The structure of transition function in Fig. 4 acts as a combinational network. Therefore, the synthesis of this transition function has to conform to the restrictions mentioned above.

Fig.4. The structure of a Reversible Sequential Circuit

There are two objectives in the reversible circuit synthesis [21].

- i. Minimize the number of gates. The number of gates gives a simple estimate of the implementation cost of a reversible circuit.

- ii. Minimize the number of garbage outputs. Minimizing the number of garbage outputs leads to minimized area and power.

## **3 RELATED WORK**

The following attempts have been made recently to design reversible T flip-flop and construct sequential circuits using them.

- i. Min-Lun Chaung et al. have proposed new gates by allowing feedback for D & T latches in 2008 [21]. These latches have been used D & T flip-flops. Both the flipflops have 5 gates, 3 garbage outputs and 2 constant inputs.

- V. Rajmohan et al. [23] have proposed T flip-flop by two Sayem Gates and one Feynman Gate in 2011. Hence 3 gates, 3 garbage outputs and 2 constant inputs have been used in constructing T flip-flop.

We observed that the gate, garbage output and constant input counts can further be reduced and it is possible to construct a T flip-flop using only one gate proposed in this paper. Accordingly low cost asynchronous and synchronous counters can be designed using proposed T flip-flop.

## 4 PROPOSED REVERSIBLE GATE AND T FLIP-FLOP

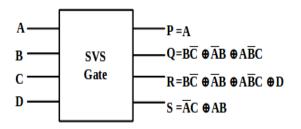

The section describes our proposed gate name "SVS" gate and T flip-flop constructed using SVS gate.

#### 4.1 PROPOSED REVERSIBLE SVS GATE

We propose a new 4\*4 reversible SVS gate. The block diagram of the proposed gate is shown in Fig.5. Its corresponding truth table is shown in table I.

Table I Truth Table of the Proposed Reversible Gate

| Α | В | С | D | Р | Q | R | S |

|---|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0 |

| 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 1 | 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 1 | 1 | 0 | 1 | 0 | 1 |

| 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

| 1 | 0 | 0 | 1 | 1 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 1 | 1 | 1 | 0 |

| 1 | 0 | 1 | 1 | 1 | 1 | 0 | 0 |

| 1 | 1 | 0 | 0 | 1 | 1 | 1 | 1 |

| 1 | 1 | 0 | 1 | 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 0 | 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 |

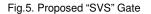

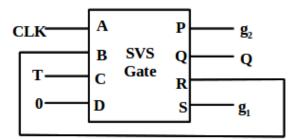

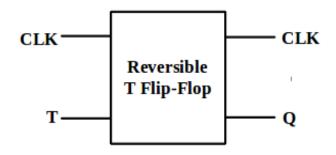

## 4.2 PROPOSED REVERSIBLE POSITIVE EDGE TRIGGERED T-FLIPFLOP

A flip-flop is a bi-stable multivibrator. A flip-flop has only two

## INTERNATIONAL JOURNAL OF SCIENTIFIC & ENGINEERING RESEARCH, VOLUME 4, ISSUE 11, NOVEMBER-2013 ISSN 2229-5518

stable states. In this section we propose the realization of T Flip-flop using our proposed reversible gate. The truth table of the T Flip- flop is given in Table II. The reversible design is shown in Fig. 6 and the corresponding block diagram is shown in Fig.7. The reversible realization of T Flip-flop has one constant input and it produces two garbage outputs. The comparison of the proposed design of T flip-flop with the existing designs is given in Table III based on three parameters namely number of gate counts, garbage outputs and constant inputs.

#### Table II Positive Edge Triggered T Flip-Flop

| CLK | Т | $\mathbf{Q}_{N-1}$ | Q |

|-----|---|--------------------|---|

| 0   | 0 | 0                  | 0 |

| 1   | 0 | 0                  | 0 |

| 0   | 0 | 1                  | 1 |

| 1   | 0 | 1                  | 1 |

| 0   | 1 | 0                  | 0 |

| 1   | 1 | 0                  | 1 |

| 0   | 1 | 1                  | 1 |

| 1   | 1 | 1                  | 0 |

Fig.6. Reversible Positive Edge Triggered T Flip-Flop

Fig.7. Block Diagram of Proposed T Flip-Flop

Table III Comparison of Different T Flip-Flops with Only Q Output

|                                 | No. of<br>Gates | Garbage<br>Outputs | Constant<br>Inputs |

|---------------------------------|-----------------|--------------------|--------------------|

| Existing[18]                    | 10              | 12                 | 10                 |

| Existing[19]                    | 5               | 3                  | 2                  |

| Existing[20]                    | 10              | 10                 | 10                 |

| Existing[21]                    | 5               | 3                  | 2                  |

| Existing[23]                    | 3               | 3                  | 2                  |

| Proposed Design                 | 1               | 2                  | 1                  |

| Improvement<br>Factor w.r.t[18] | 10              | 6                  | 10                 |

| Improvement<br>Factor w.r.t[19] | 5               | 1.5                | 2                  |

| Improvement<br>Factor w.r.t[20] | 10              | 5                  | 10                 |

| Improvement<br>Factor w.r.t[21] | 5               | 1.5                | 2                  |

| Improvement<br>Factor w.r.t[23] | 3               | 1.5                | 2                  |

## 5 DESIGN OF ASYNCHRONOUS REVERSIBLE COUNTERS

A counter, by function, is a sequential circuit consisting a set of flip-flops connected in a suitable manner to count the sequence of the input pulses presented to it in digital form. In a asynchronous counters, the output transition of one flip-flop serves as a source for triggering other flip-flops.

#### 5.1 Proposed 4-bit Asynchronous Up-Counter

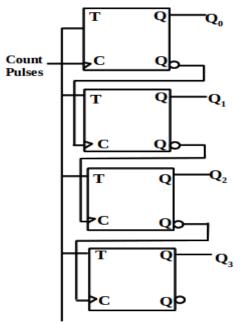

The conventional circuit diagram of a 4-bit binary asynchronous up-counter is shown in Fig. 8 [25].

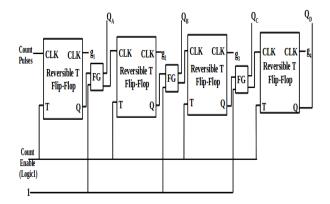

The reversible design of the 4-bit asynchronous UP-Counter is shown in Fig. 9. At the output of each reversible T Flip-flop, the Feynman Gate is used for the complemented Q output with the input B=1. These complemented Q outputs of each T Flip-flop trigger the subsequent T Flip-flops and the reversible design performs the Up-Counter operation. The comparison of the proposed design with the existing is shown in Table IV.

Count Enable(Logic1)

Fig.8. A Conventional 4-bit Asynchronous Up-Counter

Fig.9. Proposed 4-bit Reversible Asynchronous Up-Counter

Table IV Comparison Between Existing and Proposed Reversible Asynchronous UP Counter Design

|                                 | No. of Gates | Garbage<br>Outputs | Constant<br>Inputs |

|---------------------------------|--------------|--------------------|--------------------|

| Existing[23]                    | 15           | 12                 | 11                 |

| Proposed Design                 | 7            | 8                  | 7                  |

| Improvement<br>Factor w.r.t[23] | 2.14         | 1.5                | 1.57               |

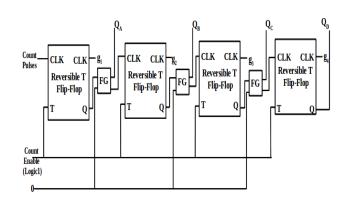

### 5.2 Proposed 4-bit Asynchronous Down-Counter

The reversible design of the above 4-bit asynchronous Down-Counter is shown in Fig. 10. At the output of each reversible T Flip-flop, the Feynman Gate is used for fan-out of Q output with the input B=0. These Q outputs of each T Flip-flop trigger the subsequent T Flip-flops and the reversible design performs the Down-Counter operation. The comparison of the proposed design with the existing is shown in Table V.

Fig.10. Proposed 4-bit Reversible Asynchronous Down-Counter

|                 | No. of Gates | Garbage<br>Outputs | Constant<br>Inputs |

|-----------------|--------------|--------------------|--------------------|

| Existing[23]    | 15           | 12                 | 11                 |

| Proposed Design | 7            | 8                  | 7                  |

| Improvement     | 2.14         | 1.5                | 1.57               |

Table V Comparison Between Existing and ProposedReversible Asynchronous Down Counter Design

Similarly, the reversible design of the 4 -bit asynchronous Up/Down counter can be proposed by reversible T flip-flop.

Factor w.r.t[23]

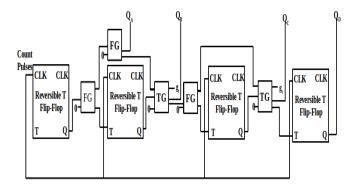

# 6 DESIGN OF SYNCHRONOUS REVERSIBLE COUNTERS

The asynchronous counters above are simple but not very fast. If a counter with a larger number of bits is constructed in this manner, then the delays caused by the cascaded clocking scheme may become too long to meet the desired performance requirements. We can build a faster counter by clocking all flipflops at the same time as presented below. Synchronous counters have regular pattern and can be constructed using flip-flops and gates.

#### 6.1 Proposed 4-bit Synchronous Up-Counter

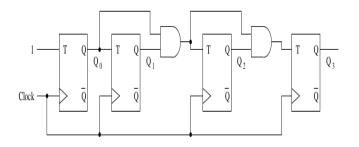

A conventional 4-bit Up Synchronous Counter can be realized as shown in Fig.11 [26]. In Fig. 11, instead of using AND gates of

increased size for each stage, we use a factored arrangement. This arrangement does not slow down the response of the counter, because all flip-flops change their states after a propagation delay from the positive edge of the clock .Note that a change in the value of  $Q_0$  may have to propagate through several AND gates to reach the flip-flops in the higher stages of the counter, which requires a certain amount of time [26]. This time must not exceed the clock period. Actually, it must be less than the clock period minus the setup time of the flip-flops.

Fig.11. A Conventional 4-bit Synchronous Up-Counter

The reversible design of the 4-bit Synchronous UP-Counter is shown in Fig. 12. The Toffoli gate is used to realize the AND function. Feynman Gate is used for the fan-out of Q output with the input B=0. The comparison of the proposed design with the existing is shown in Table VI.

Fig.12. Proposed 4-bit Reversible Synchronous UP Counter

Table VI Comparison Between Existing and Proposed Reversible Synchronous Up Counter Design

|                                 | No. of Gates | Garbage<br>Outputs | Constant<br>Inputs |

|---------------------------------|--------------|--------------------|--------------------|

| Existing[23]                    | 15           | 12                 | 13                 |

| Proposed Design                 | 9            | 10                 | 9                  |

| Improvement<br>Factor w.r.t[23] | 1.66         | 1.2                | 1.44               |

Similarly, the reversible design of the 4 -bit synchronous down and Up/Down counter can be proposed by reversible T flip-flop.

### **7 CONCLUSION**

In this work, we propose a novel reversible gate which has shown the significant improvement for realizing and optimizing T flipflop. We also propose the designs of reversible asynchronous and synchronous counter using reversible T flip-flop, Feynman Gate and Toffoli Gate. The designs of the counters are compared with existing counter design for three parameters namely gate count, garbage output, constant inputs and found improvement by a factor of 1 to 3. The proposed asynchronous and synchronous counter designs have the applications in building reversible Jonshan counter, Ring Counter, ASM charts and reversible processor etc. This work will provide a new face in designing of large and complex reversible sequential circuits for quantum computers. The design can further be extended to develop efficient reversible counters and reversible sequential circuits as a further work.

### REFERENCES

- R. Landauer, "Irreversibility and heat generation in the computing process", IBM J. Research and Development, Vol.5, Issue 3, July, 1961, pp. 183-191

- [2] R. W. Keyes and R. Landauer, "Minimal energy dissipation in logic," IBM J. Research and Development, Vol. 14, Issue 2, March 1970, pp. 152-157

- [3] C.H. Bennett, "Logical Reversibility of Computation", IBM J. Research and Development, Vol. 17, Issue 6, November 1973, pp. 525-532

- [4] Notes on Landuer's principle, reversible computation and Maxwell's Demon, C.H. Bennet, Studies in History and Philosophy of Modern Physics, Vol. 34, October 2002, pp. 501-510

- [5] T. Toffoli," Reversible computing". Tech rep, MIT/LCS/TM-151, MIT Lab for Computer Science, 1980, pp.632-644.

- [6] R. Feynman, "Quantum Mechanical Computers," Optical News, 1985, pp. 11-20.

- [7] E. Fredkin and T. Toffoli, "Conservative logic", MIT/LCS/TS-545, Cambridge, Massachusetts, 1982, pp.219-255.

- [8] D. P. Vasudevan, "Reversible-logic design with online testability", IEEE Trans, Instru and Meas., Vol. 55, Issue 2, April 2006, pp.406– 414.

- [9] Mehdi Saeedi and Igor L. Markov, "Synthesis and Optimization of Reversible Circuits - A Survey," arXiv: 1110.2574v2 [cs.ET], 20 Mar 2013, pp. 1-34.

- [10] Robert Wille, Sebastian Offermann and Rolf Drechsler, "SyReC: A Programming Language for Synthesis of Reversible Circuits", Specification & Design Languages (FDL), Southampton, UK, September 2010, pp1-6.

- [11] D.M. Miller, D. Maslov and G.W. Dueck, "A transformation based algorithm for reversible logic synthesis", DAC Conf., Anaheim, CA, 2003, pp. 318-323.

- [12] P. Gupta, A. Agrawal and N. Jha, "An algorithm for synthesis of reversible logic circuits", IEEE Trans. on CAD ,Vol. 25, Issue 11, November 2006, pp. 2317-2330.

- [13] V.V. Shende, A.K. Prased, I.L. Markov and J.P. Hayes, "Synthesis of reversible logic circuits", IEEE Trans on CAD of ICS, Vol. 22, Issue 6, 28 May 2003, pp. 710-722.

## INTERNATIONAL JOURNAL OF SCIENTIFIC & ENGINEERING RESEARCH, VOLUME 4, ISSUE 11, NOVEMBER-2013 ISSN 2229-5518

- [14] R. Wille and R. Drechsler, "BDD-based synthesis of reversible logic for large functions", Design Autom, 46<sup>th</sup> ACM /IEEE Conf., 26 July 2009, pp. 270-275.

- [15] Md. Saiful Islam, M.M. Rahman, Zerina Begum and M.Z. Hafiz, "Fault Tolerant Variable Block Carry Skip Logic (VBCSL) Using Parity Preserving Reversible Gates", International Journal of Computer and Electrical Engineering, Vol.3, No.1, February 2011, Singapore, pp. 1– 7.

- [16] Anugrah Jain and Sushil Chandra Jain, "Towards Implementation of Fault Tolerant Reversible Circuits", 1st IEEE International Conference on Emerging Trends and Applications in Computer Science (ICETACS), Shilong, Meghalaya, India, Sept. 2013, pp.86-91.

- [17] Anindita Banerjee and Anirban Pathak, "On the Synthesis of Sequential Reversible Circuit," arXiv: 0707.4233v1 [quant-ph.], 28 July 2007, pp. 1–9.

- [18] H. Thapiyal and M.B. Srinivas, "A Beginning in the Reversible Logic Synthesis of Sequential Circuits," Proceedings of Military and Aerospace Programmable Logic Devices International Conference, 2005, pp.1-5

- [19] SKS Hari, S Shroff, SK Noor Mahammad and V. Kamakoti,"Efficient Building Blocks for Reversible Sequential Circuit design," 49<sup>th</sup> IEEE International Midwest Symposium on Circuits and Systems, Vol.1, 2006, pp. 437-441.

- [20] J.E. Rice, "A New Look at Reversible Memory Elements,"

Proceedings of IEEE International Symposium on Circuits and Systems, Lethbridge Univ., Alta, May 2006.

- [21] Min-Lun Chuang and Chun-Yao Wang , "Synthesis of Reversible Sequential Elements", ACM Journal on Emerging Technologies in Computing Systems, Vol. 3, No. 4, Article 19, January 2008, pp. 1-19.

- [22] Abu Sadat, Md. Sayem and Masashi Ueda, "Optimization of Reversible Sequential Circuits," Journal of Computing, vol.2, issue 6, 2010, pp. 208-214.

- [23] V. Rajmohan and Dr. V. Ranganathan, "Design of Counters Using Reversible Logic", 3rd International Conference of Electronics Computer Technology (ICECT), Vol.5, 2011, pp. 138-142.

- [24] H.M.H. Babu, M.R. Islam, S.M.A. Chowdhury and A.R. Chowdhury, "Synthesis of Full-adder Circuit Using Reversible Logic," Proceedings of 17th International Conference on VLSI Design, January 2004, pp.757-760.

- [25] M. Morris Mano, Michael D. Ciletti," Digital Design," Fourth edition, Pearson Education, pp. 268-288.

- [26] Lecture Notes on CSE Introduction to Digital Systems, Supplementary Reading, "Counters with T Flip-Flops", pp. 1-4.