## Design of 64 Bit UCSLA for Low Power VLSI Application

K. Jancy Beryl<sup>1</sup>, A. Beno<sup>2</sup> <sup>1</sup>PG Scholar, VLSI Design, Department of ECE <sup>2</sup>Assistant Professor (S.G), Department of ECE <sup>1&2</sup>Dr. Sivanthi Aditanar College of Engineering, Tiruchendur, <sup>1</sup>jancyberyl@gmail.com, <sup>2</sup>beno\_csi@yahoo.com

**Abstract**— This paper presents area and power efficient carry select adder (CSLA). This uses an uniform sized CSLA (UCSLA) with carry skip adder (CSKA)  $C_{in}$ =1 instead of using Ripple Carry Adder (RCA) with  $C_{in}$ =1. The delay is reduced using CSKA. The achieved area and power of the proposed UCSLA is 1412  $\mu$ m<sup>2</sup> and 0.0456 mW. The delay is decreased to 47.176 ns.

\_\_\_\_\_

Index Terms – UCSLA, CSKA, RCA, BEC, Multiplexer, Area, Power, Delay, Verilog-HDL Simulation.

\_\_\_\_ **♦**

#### **1** INTRODUCTION

A DDITION is basic operation used in many data path logic systems such as adders, multipliers etc. Carry select adder is used for high speed operation by reducing the carry propagation delay. Carry select adders generates many carries and partial sum. The final carry out is selected by the set of multiplexers [1].

The proposed method is to use carry skip adder (CSKA) instead of one ripple carry adder (RCA) with C<sub>in</sub>=0 in the variable sized CSLA structure to make uniform sized CSLA to consume lower area, power and high speed.

Adders are widely used in all electronic applications for example digital signal processing, microprocessors, and microcontrollers. The key process of the VSLI designer was to reduce the area, power and delay [2].

Carry Select Adder (CSLA) is one of the fastest adders used in many data-processing processors to perform fast arithmetic functions. Ripple carry adders are the slowest even though they are compact in design. Whereas carry look-ahead is the fastest one but consumes more area [3].

The CSLA uses multiple pairs of RCA to generate partial sum and carry by considering carry input C<sub>in</sub>=0 and C<sub>in</sub>=1, then the final sum and carry are selected by the multiplexers. It is consider to be area inefficient [4]. The digital adders suffer with the problem of carry propagation delay and also power dissipation is one of the most important design objectives in integrated circuits, after speed [5]. The multiplexer is used to obtain expected output according to the logic state of carry-in signal. The carry select adder achieves low power and area efficiency with an increase in delay [6].

Modified CSLA shows reduction in area and power consumption in comparison with conventional CSLA with a higher delay. The result shows that the Proposed CSLA is better than modified CSLA (MCSLA) [7]. Two types of carry select adder (CSLA) are used to reduce the area and power. One is variable sized carry select adder (VCSLA) and the other is uniform sized carry select adder (UCSLA). The variable sized carry select adder (VCSLA) is used to increase the BEC, so the number of gates is increased [8, 9].

The concept of uniform sized carry select adder (UCSLA) is used to reduce the area, power and delay. In this paper, we proposed the UCSLA with 64 bit inputs.

#### 2 VARIABLE SIZED CARRY SELECT ADDER (VCSLA)

A 64 bit VCSLA is developed. In this VCSLA, RCA is used in upper adder and BEC circuit is used in lower adder part. The VCSLA is used to increase the BEC, so the number of gates is increased.

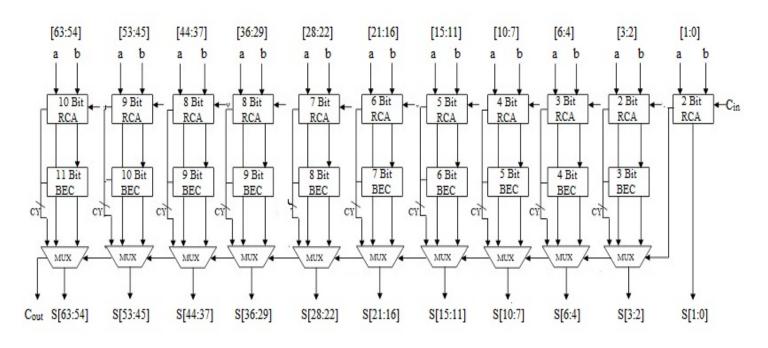

The 64 bit VCSLA architecture is shown in Fig. 1. It has eleven groups of different size CSLA. The delay and area evaluation of each group are shown in Fig. 2.

The group 1 has only one set of 2 bit RCA with carry-in signal. The carry-out of the RCA is used as control signal in multiplexer.

The group 2 has one set of 2 bit RCA with  $C_{in}=0$  and one set of 3 bit BEC instead of 2 bit RCA with  $C_{in}=1$ . The 2 bit RCA with  $C_{in}=0$  is the upper adder and 3 bit BEC is lower adder. The 2 bit input of a and b is given to the upper adder. The output of the upper adder is given to 3 bit BEC circuit and multiplexer. The multiplexer is used to select the output either upper adder or lower adder according to the control signal  $C_{in}$ ( $C_1$ ). Now the sum  $S_2$  and carry-out  $C_3$  is obtained.

Similarly, the other groups are evaluated from the above explanation.

The area and delay of VCSLA is tabulated in Table 1.

Fig. 1 Sixty Four Bit Regular CSLA Architecture

Fig. 2 (a) Group 2 Architecture

Sum 5 Fig. 2 (b) Group 3 Architecture

Sum 4

C,

10:5 Mux[3]

Sun 6

FA

C,

Fig. 2 (c) Group 3 Architecture Fig. 2 (d) Group 4 Architecture

Fig. 2 Delay and area evaluation of VCSLA: (a) group2, (b) group3, (c) group4 and (d) group5. FA is a Full Adder.

| i |                                |               |  |  |  |  |  |

|---|--------------------------------|---------------|--|--|--|--|--|

|   | TABLE 1<br>AREA COUNT OF VCSLA |               |  |  |  |  |  |

|   | Word Size                      | Area (in µm²) |  |  |  |  |  |

|   | 8 Bit                          | 179           |  |  |  |  |  |

| Word Size | Area (in µm²) |

|-----------|---------------|

| 8 Bit     | 179           |

| 16 Bit    | 399           |

| 32 Bit    | 839           |

| 64 Bit    | 1552          |

|           |               |

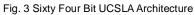

### 3 UNIFORM SIZED CARRY SELECT ADDER (UCSLA)

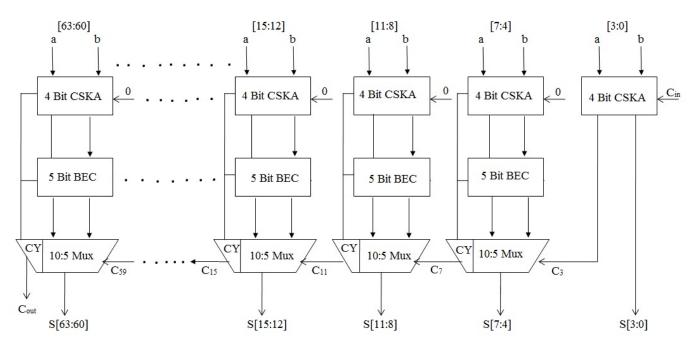

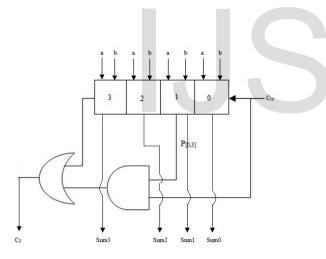

In his UCSLA, carry skip adder (CSKA) is used for reducing del w and area compared with VCSLA. The upper adder has the CSKA with  $C_{in}$ =0 and the BEC circuit is in the lower ad er instead of RCA with Cin=1 in the UCSLA. The 64 bit UC 5LA architecture is shown in Fig. 3. The group1 and 2 arc nitecture of UCSLA are shown in Fig. 4 and Fig. 5. The CS (A is used to reduce the delay compared with RCA.

The group 1 has only one set of 4 bit CSKA with carry-in sig tal. The carry-out of the CSKA is used as control signal in multiplexer.

The group 2 has one set of 4 bit CSKA with Cin=0 and

> one set of 5 bit BEC instead of 4 bit CSKA with C<sub>in</sub>=1.

Fig. 4 Four Bit CSKA Architecture

TABLE 2 AREA COUNT OF UCSLA

| i | Word Size | Area (in μm²) |

|---|-----------|---------------|

|   | 8 Bit     | 162           |

|   | 16 Bit    | 295           |

|   | 32 Bit    | 816           |

|   | 64 Bit    | 1412          |

|   |           |               |

Fig. 5 Group2 UCSLA Architecture

The 4 bit CSKA with  $C_{in} = 0$  is the upper adder and 5 bit BEC is USER © 2013 http://www.ijser.org

| Messages             |                                         |          |           |           |           |           |           |           |     |

|----------------------|-----------------------------------------|----------|-----------|-----------|-----------|-----------|-----------|-----------|-----|

|                      | 111111111111111111111111111111111111111 | 10101010 | 101010101 | 010111111 | 111101101 | 01010101  | 010101010 | 111111111 | 101 |

| . <b></b> , /csa64/b | 111111111111111111111111111111111111111 | 10110101 | 101101011 | 011111101 | 011010101 | 10101101  | 101011011 | 111101011 | 010 |

| 🔶 /csa64/cin         | St0                                     |          |           |           |           |           |           |           |     |

| 🛨 🥎 /csa64/sum       | 111111111111111111111111111111111111111 | 01100000 | ¢11000000 | 110111101 | 01100001  | 100000011 | 000000110 | 111101010 | 111 |

| /csa64/cout          | St1                                     |          |           |           |           |           |           |           |     |

Fig. 5 Simulation Results of CSLA in Modelsim

| Word<br>Size | Adder | Area (in<br>μm²) | Delay (in<br>ns) | Power (in<br>mW) |

|--------------|-------|------------------|------------------|------------------|

| 8-bit        | VCSLA | 179              | 30.965           | 0.0247           |

|              | UCSLA | 162              | 28.198           | 0.0116           |

| 16-bit       | VCSLA | 399              | 33.158           | 0.0452           |

|              | UCSLA | 295              | 30.008           | 0.0218           |

| 32-bit       | VCSLA | 839              | 38.432           | 0.0691           |

|              | UCSLA | 816              | 32.516           | 0.0386           |

| 64-bit       | VCSLA | 1552             | 49.218           | 0.1016           |

|              | UCSLA | 1412             | 47.176           | 0.0456           |

TABLE 3 COMPARISONS BETWEEN VCLSA AND UCSLA

lower adder. The 4 bit input of a and b is given to the upper adder. The output of the upper adder is given to 5 bit BEC

circuit and multiplexer. The multiplexer is used to select the output either upper adder or lower adder according to the

control signal  $C_{in}$  (C<sub>3</sub>). Now the sum  $S_2$  and carry-out  $C_3$  is obtained.

| {C <sub>6</sub> , Sum [6:4]}     | = | C <sub>3</sub> + Multiplexer  |

|----------------------------------|---|-------------------------------|

| {C <sub>10</sub> , Sum [10:7]}   | = | C <sub>6</sub> + Multiplexer  |

| {C <sub>out</sub> , Sum [15:11]} | = | $C_{10}$ + Multiplexer        |

| {C <sub>out</sub> , Sum [21:16]} | = | C <sub>15</sub> + Multiplexer |

| {C <sub>out</sub> , Sum [31:22]} | = | C <sub>21</sub> + Multiplexer |

|                                  |   |                               |

Similarly, the other groups are evaluated from the above explanation. The total number of area counts of UCSLA is tabulated in Table 2.

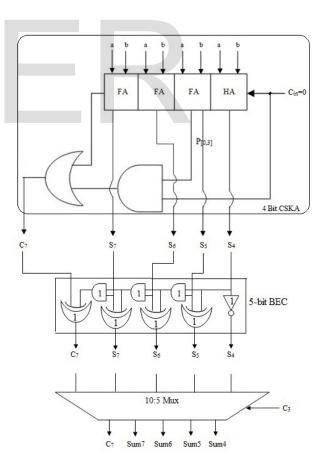

#### **4** SIMULATION RESULTS AND DISCUSSION

This work has been simulated using Verilog-HDL (Modelsim) in Fig. 5. The adders (of various size 16, 32, 64-bit) are designed and simulated using Modelsim. All the V files (Regular and Modified) are also simulated in Modelsim and corresponding results are compared. After simulation the different size codes are synthesized using Xilinx ISE 9.1i.

The simulated V files are imported into the synthesized tool and corresponding values of delay and area are noted. The synthesized reports contain area and delay values for different sized adders. The similar design flow is followed for both the VCSLA and UCSLA.

Table 3 shows the area and power of the UCSLA significantly reduced by 1412  $\mu$ m<sup>2</sup> and 0.0456 mW respectively. The delay also reduced to 47.176 ns. The proposed UCSLA architecture is low power, low area, decreased in delay, simple and efficient.

#### 5 CONCLUSION

In this paper, UCSLA is designed by using single carry skip adder (CSKA) and binary to excess-1 converter (BEC) instead of using one set of ripple carry adder (RCA) with  $C_{in}$ =0 to reduce area and power with increase in delay. The compared results show that reducing area and power is 1412  $\mu$ m<sup>2</sup> and 0.0456 mW. The reduced delay is 47.176 ns. The UCSLA architecture is low area, low power, simple and efficient for VLSI applications.

#### REFERENCES

- Bedrij O. J, "Carry-select adder," IRE Transaction on Electronic Computers, pp.340–344, 1962.

- [2] Allipeera K, Ahmed Basha S, "An Efficient 64-Bit Carry Select Adder With Less Delay And Reduced Area Application," *International Journal* of Engineering Research and Applications, Vol. 2, Issue 5, pp.550-554, 2012.

- [3] Wang, Y. Pai, C.Song, X., "The design of hybrid carry look-ahead/ carry-select adders," *Circuits and Systems II: Analog and Digital Signal Processing, IEEE Transactions* on Volume 49, pp.16-24, 2002.

International Journal of Scientific & Engineering Research, Volume 4, Issue 5, May-2013 ISSN 2229-5518

- [4] A. Tyagi," A reduced area scheme for carry-select adders", IEEE Transaction on Computer, vol. 42, pp. 1163-1170, 1993.

- [5] Ceiang T. Y and Hsiao M. J, "Carry-select adder using single ripple carry adder," *Electronics Letters*, vol. 34, no. 22, pp. 2101–2103, October 1998.

- [6] Kim Y and L-S Kim, "64-bit carry-select adder with reduced area," *Electronics Letters*, vol. 37, pp. 614-615, May 2001.

- [7] Deepthi Obul Reddy, Ramesh Yadav P, "Carry Select Adder with Low Power and Area Efficiency," *International Journal of Engineering Research and Development*, Volume 3, Issue 3, pp. 29-35, 2012.

- [8] Ram Kumar B, Kittur H. M, and P. M. Kannan, "ASIC implementation of modified faster carry save adder," *European Journal of Scientific Research*, vol. 42, no. 1, pp. 53–58, 2010.

- [9] Ram Kumar B and Kittur H.M, "Low-Power and Area-Efficient Carry Select Adder," *IEEE transactions on very large scale integration (VLSI)* systems, vol. 20, no. 2, February 2012.

# IJSER